# PONTIFICIA UNIVERSIDAD CATOLICA DE CHILE SCHOOL OF ENGINEERING

# SLICE-BASED ANALOG DESIGN AND ITS APPLICATION TO PARTICLE PHYSICS INSTRUMENTATION

### PABLO WALKER GALDAMES

Thesis submitted to the Office of Research and Graduate Studies in partial fulfillment of the requirements for the degree of Master of Science in Engineering

Advisor:

ANGEL ABUSLEME HOFFMAN JUAN PEDRO OCHOA-RICOUX

Santiago de Chile, June 2021

© MMXXI, PABLO WALKER GALDAMES

# PONTIFICIA UNIVERSIDAD CATOLICA DE CHILE SCHOOL OF ENGINEERING

# SLICE-BASED ANALOG DESIGN AND ITS APPLICATION TO PARTICLE PHYSICS INSTRUMENTATION

#### PABLO WALKER GALDAMES

Members of the Committee:

ANGEL ABUSLEME HOFFMAN

JUAN PEDRO OCHOA-RICOUX

MATÍAS NEGRETE PINCETIC Hates Negrale Frank C

KRZYSZTOF HERMAN

JUAN CARLOS HERRERA MALDONADO

Thesis submitted to the Office of Research and Graduate Studies in partial fulfillment of the requirements for the degree of Master of Science in Engineering

Santiago de Chile, June 2021

© MMXXI, PABLO WALKER GALDAMES

#### **ACKNOWLEDGEMENTS**

First, I would like to thank professor Angel Abusleme, one of my co-advisors. Angel taught me most of what I know about microelectronics, and has guided me throughout the research process with his knowledge, enthusiasm and his endless patience. Without him, this thesis would not have been possible, and quite likely I would have never designed or been involved with integrated circuits.

Second, I would like to thank professor Pedro Ochoa, my other co-advisor. Pedro introduced me to the area of experimental physics, and provided me with opportunities to participate in the design of particle physics instrumentation, beyond the present thesis, and has believed in me and my abilities as an engineer. His support has been invaluable over the years.

Finally, I would like to thank my parents for their love, support, understanding and patience throughout this long process, for which I am eternally grateful.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                 | iii   |

|--------------------------------------------------|-------|

| TABLE OF CONTENTS                                | iv    |

| LIST OF FIGURES                                  | ix    |

| LIST OF TABLES                                   | xvi   |

| ABSTRACT                                         | xvii  |

| RESUMEN                                          | xviii |

| 1. INTRODUCTION                                  | 1     |

| 1.1 Analog integrated circuit design             | 1     |

| 1.1.1 The design process                         | 1     |

| 1.1.2 About systematization and automation       | 2     |

| 1.2 Topics covered by the Thesis                 | 3     |

| 1.3 Particle physics experiments                 | 4     |

| 1.4 Electronics for particle physics experiments | 6     |

| 1.4.1 Detector                                   | 6     |

| 1.4.2 Amplifier                                  | 7     |

| 1.4.3 Pulse Shaper                               | 8     |

| 1.4.4 Digitizer                                  | 8     |

| 1.5 Noise in electronics                         | 9     |

| 1.6 The $g_m/I_D$ design methodology             | 11    |

| 1.6.1 The $g_m/I_D$ ratio as a design variable   |       |

| 1.6.2 Methodology                                | 13    |

| 1.7 Thesis content                               | 15    |

| 2. SLICE-BASED DESIGN METHODOLOGY                | 16    |

| 2.1 Introduction                                 | 16    |

| 2.2 Th   | e effects of connecting circuits in parallel           | 17 |

|----------|--------------------------------------------------------|----|

| 2.2.1    | The general case                                       | 17 |

| 2.2.2    | Single-pole amplifier                                  | 18 |

| 2.2.3    | Noise analysis                                         | 19 |

| 2.3 Th   | e design methodology                                   | 20 |

| 2.3.1    | The pre-design stage                                   | 20 |

| 2.3.2    | The design stage                                       | 22 |

| 2.3.3    | Adjustable performance                                 | 23 |

| 2.3.4    | Potential issues                                       | 23 |

| 3. NOISE | ANALYSIS IN CHARGE-SENSITIVE AMPLIFIERS                | 25 |

| 3.1 Int  | roduction                                              | 25 |

| 3.2 Eq   | uivalent noise charge                                  | 25 |

| 3.2.1    | Front-end circuit model                                | 26 |

| 3.2.2    | Single-electron output power                           | 27 |

| 3.2.3    | Output noise power                                     | 29 |

| 3.2.4    | The ENC equation                                       | 31 |

| 3.3 Fil  | ter design                                             | 31 |

| 3.3.1    | Noise coefficients                                     | 31 |

| 3.3.2    | Normalized noise coefficients                          | 32 |

| 3.4 Ch   | arge-sensitive amplifier design                        | 36 |

| 3.4.1    | The $g_m/I_D$ methodology and noise analysis           | 36 |

| 3.4.2    | Charge amplifier noise using the $g_m/I_D$ methodology | 37 |

| 3.4.3    | Capacitance matching for constant $g_m/I_D$            | 39 |

| 3.4.4    | Flicker noise and corner frequency                     | 40 |

| 3.4.5    | Minimum noise versus $g_m/I_D$ and peaking time        | 43 |

| 3.4.6    | White-noise dominance – practical design guidelines    | 45 |

| 3.4.7    | Noise analysis in slice-based design                   | 48 |

| 4. EFFEC | TS OF DEVICE MISMATCH ON SLICE-BASED DESIGN            | 50 |

| 4.1 In  | ntroduction                                                                | 50 |

|---------|----------------------------------------------------------------------------|----|

| 4.2 N   | Mismatch model                                                             | 51 |

| 4.3 N   | Mismatch parameters                                                        | 52 |

| 4.4 P   | Physical interpretation of the distance term in Pelgrom's mismatch model . | 54 |

| 4.5 D   | Device mismatch in cell-based design                                       | 55 |

| 4.5.1   | Parameter variation model                                                  | 55 |

| 4.5.2   | Parameter scaling                                                          | 57 |

| 4.6 A   | simple example of noise scaling in the presence of device mismatch         | 60 |

| 4.7 N   | Monte Carlo simulations                                                    | 62 |

| 4.7.1   | Methodology                                                                | 63 |

| 4.7.2   | Results – Single device noise scaling                                      | 64 |

| 4.7.3   | Results – Charge-sensitive amplifier                                       | 68 |

| 4.7.4   | Mismatch and switches – The charge-sensitive amplifier of the Heisenberg   |    |

|         | IC                                                                         | 76 |

| 5. SYST | TEM-LEVEL DESIGN                                                           | 77 |

| 5.1 In  | ntroduction                                                                | 77 |

| 5.2 S   | ystem block diagram                                                        | 77 |

| 5.2.1   | The Heisenberg chip block diagram                                          | 79 |

| 5.3 S   | ystem specifications                                                       | 80 |

| 6. CIRC | UIT-LEVEL DESIGN                                                           | 82 |

| 6.1 In  | ntroduction                                                                | 82 |

| 6.2 C   | Charge-sensitive amplifier design                                          | 82 |

| 6.2.1   | Amplifier static error and nonlinearity                                    | 82 |

| 6.2.2   | Frequency response                                                         | 83 |

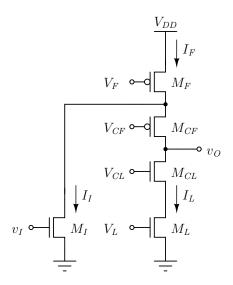

| 6.2.3   | The folded-cascode amplifier                                               | 85 |

| 6.2.4   | Equivalent transconductance, output resistance and open-loop gain          | 86 |

| 6.2.5   | Input-referred noise                                                       | 88 |

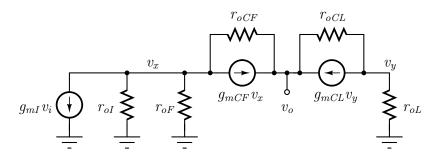

| 6.2.6   | Design parameters                                                          | 89 |

| 6.2.7    | Folded-cascode bias circuit                     |

|----------|-------------------------------------------------|

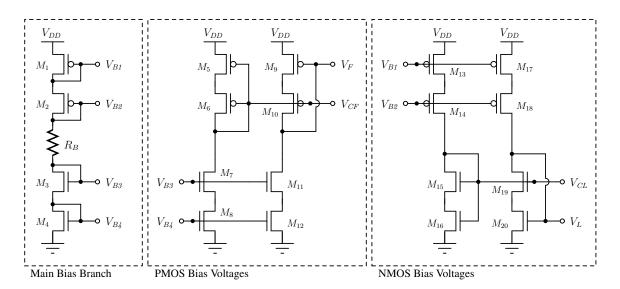

| 6.2.8    | Slice parallel connection                       |

| 6.2.9    | Feedback network                                |

| 6.3 Pre  | e-charger circuit                               |

| 6.4 Pu   | se-shaping filter                               |

| 7. IMPLE | MENTATION                                       |

| 7.1 Int  | roduction                                       |

| 7.2 Th   | e Heisenberg chip layout                        |

| 7.2.1    | Floorplan                                       |

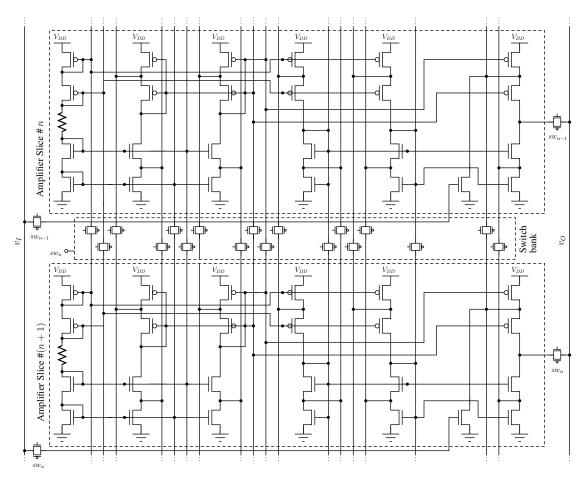

| 7.2.2    | Amplifier slice and parallel connection         |

| 7.2.3    | Feedback network, pre-charger and output buffer |

| 7.3 He   | isenberg Test PCB                               |

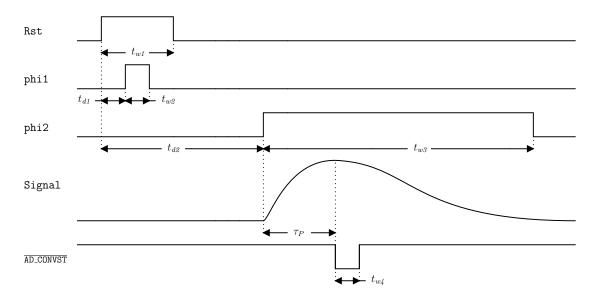

| 7.4 Fir  | mware and data sampling                         |

|          |                                                 |

|          | RESULTS                                         |

|          | roduction                                       |

|          | ise PSD and bandwidth scaling                   |

| 8.3 Inp  | out stimuli and noise measurements              |

| 8.4 Pag  | l leakage, feedback reset and baseline          |

| 8.5 Tes  | st methodology                                  |

| 8.6 CS   | A step response                                 |

| 8.6.1    | Setup                                           |

| 8.6.2    | Results                                         |

| 8.6.3    | The baseline                                    |

| 8.6.4    | Step Amplitude                                  |

| 8.6.5    | Bandwidth                                       |

| 8.7 Fil  | ter output                                      |

| 8.8 No   | ise measurements                                |

| 0 0 1    | Cotue                                           |

| 8.8.2    | Results                             | 27 |

|----------|-------------------------------------|----|

| 8.8.3    | Noise magnitude and thermal noise   | 29 |

| 8.8.4    | Flicker noise                       | ;1 |

| 8.8.5    | Noise scaling                       | ,4 |

| 8.9 Su   | mmary of design flaws               | 5  |

| 9. CONC  | LUSION                              | 57 |

| 9.1 Su   | mmary                               | ;7 |

| 9.2 Fu   | ture work                           | 8  |

| REFEREN  | CES                                 | ŀC |

| ANNEXES  |                                     | 16 |

| A Second | Lorder transfer function of the CSA | 17 |

## LIST OF FIGURES

| 1.1 | High-level view of the analog or mixed-signal design flow (Gielen and Rutenbar                                                                                                                                                            |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | (2000))                                                                                                                                                                                                                                   | 2  |

| 1.2 | Cut-away view of the ATLAS detector (ATLAS Collaboration (2008))                                                                                                                                                                          | 5  |

| 1.3 | Block diagram for a single channel of a generic pulse processing circuit for particle physics experiments                                                                                                                                 | 6  |

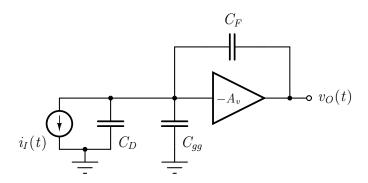

| 1.4 | Front-end amplifier for particle physics instrumentation using a charge-sensitive amplifier. The charge generated by the detector is integrated on the feedback capacitor of the voltage amplifier to obtain a voltage step at the output | 7  |

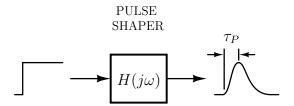

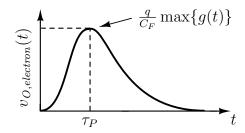

| 1.5 | Pulse shaping action done by the filter. The filter sets the peaking time $\tau_P$ , which in turn sets the conflicting requirements of noise bandwidth and system speed                                                                  | 8  |

| 1.6 | Equivalent representation of a noisy linear circuit as a noiseless linear circuit with external noise generators, referred to a single arbitrary port                                                                                     | 10 |

| 1.7 | $g_m/I_D\ vs.$ normalized drain current $I_\square$ for different values of $L$ on a 0.5- $\mu m$ technology. Data points obtained from LTspice simulations using BSIM3 MOSFET models                                                     | 13 |

| 1.8 | Relevant design ratios $v.s.$ $g_m/I_D$ for different values of $L$ on a 0.5- $\mu m$ technology. Data points obtained from LTSpice simulations using BSIM3 MOSFET models                                                                 | 14 |

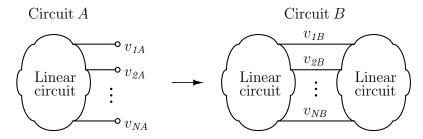

| 2.1 | Illustration of the parallel connection of identical copies of a circuit                                                                                                                                                                  | 17 |

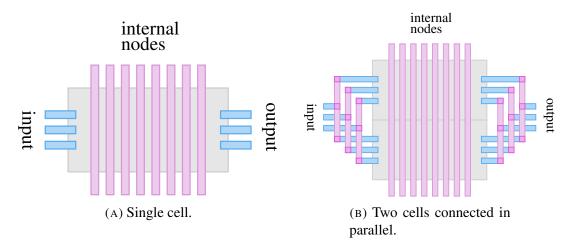

| 2.2 | Proposed layout design and parallel-connection scheme.                                                                                                                                                                                    | 22 |

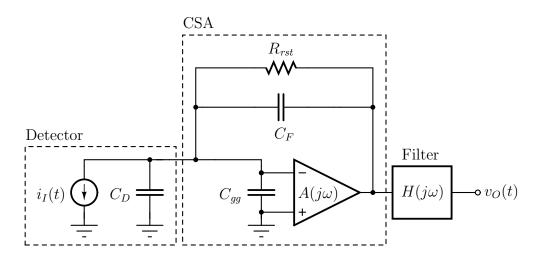

| 3.1 | Schematic representation of a typical front-end circuit in particle physics experiments. The schematic includes the circuit models for the detector, the charge-sensitive amplifier, and the pulse-shaping filter.                        | 26 |

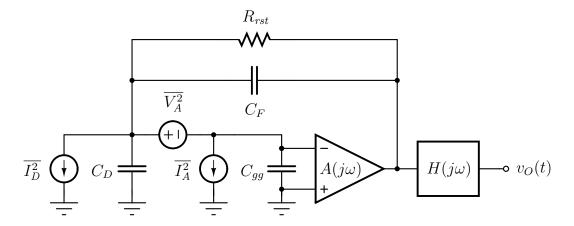

| 3.2  | Schematic for noise analysis. Noise sources from two devices are considered:                   |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | shot noise from the detector; and amplifier noise, represented as both voltage                 |    |

|      | and current noise. The amplifier noise includes both thermal and flicker noise                 |    |

|      | processes                                                                                      | 28 |

| 3.3  | Graphical representation of the pulse shaper output for a single electron of input             |    |

|      | charge, considering an arbitrary pulse shape. The maximum value of the signal                  |    |

|      | is reached at time $t=	au_P$                                                                   | 29 |

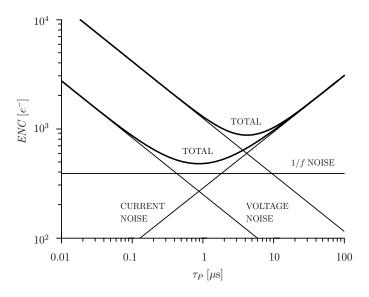

| 3.4  | Equivalent noise charge $vs.$ shaping time. The plot shows two equivalent $ENC$                |    |

|      | curves to illustrate the effect of the $1/f$ noise over the voltage noise. (Spieler            |    |

|      | (2005))                                                                                        | 35 |

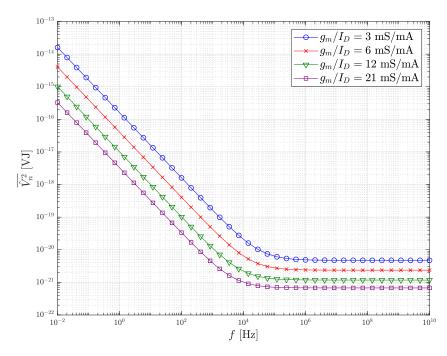

| 3.5  | Example of the normalized noise spectra for a single transistor including white                |    |

|      | and flicker noise, for different values of $g_m/I_D$ . Relevant simulation parameters          |    |

|      | are $L=0.6~\mu\mathrm{m}$ and HSPICE NMOS parameter $K_F=10^{-30}$                             | 38 |

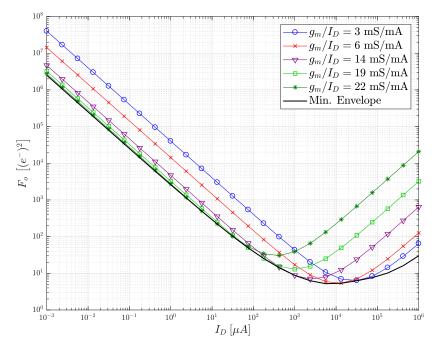

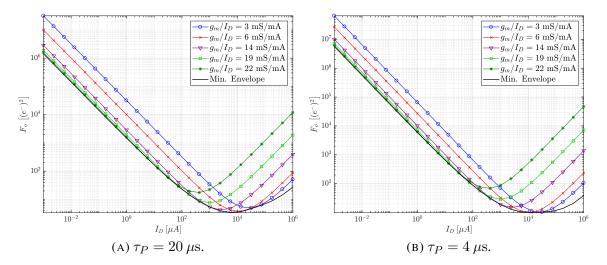

| 3.6  | $F_o$ as a function of $I_D$ . Several values of $g_m/I_D$ are plotted. A global minimum       |    |

|      | envelope curve, obtained numerically using $g_m/I_D$ values ranging from 1 to $24$             |    |

|      | is also included. Both white and flicker noise sources are considered. Relevant                |    |

|      | simulation parameters include $L=0.6~\mu\mathrm{m}$ and MOSFET SPICE model $K_F=$              |    |

|      | $10^{-30}$ . Other parameters include the use of a RU-2 filter, $\tau_P=10~\mu \mathrm{s}$ and |    |

|      | $C_K = 1 \text{ pF.}$                                                                          | 41 |

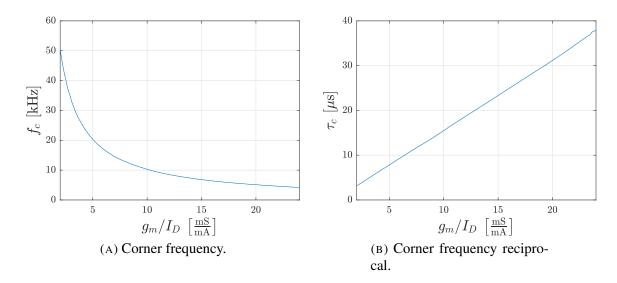

| 3.7  | Corner frequency and the reciprocal time constant for a flicker exponent of                    |    |

|      | $A_F=1$ in a $0.5$ - $\mu$ m technology                                                        | 42 |

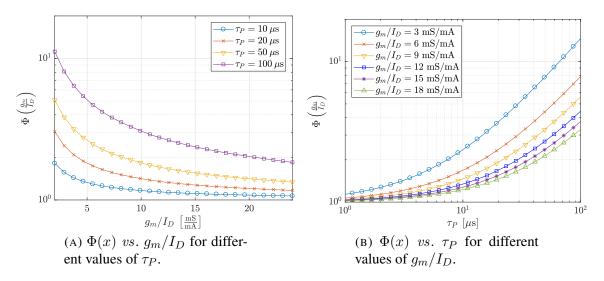

| 3.8  | Relative effect of flicker noise on the total output noise. Flicker exponent                   |    |

|      | $A_F=1$ and RU-2 filter noise coefficients were considered                                     | 43 |

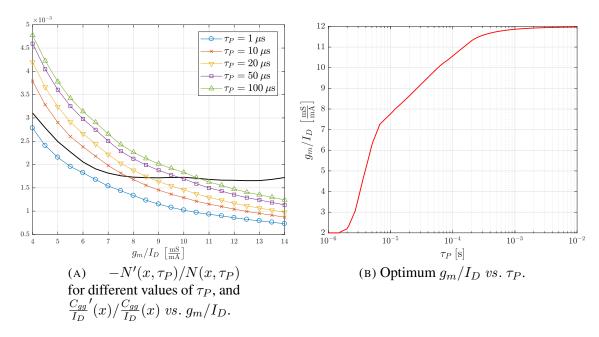

| 3.9  | Value of $g_m/I_D$ for overall minimum noise when the capacitance matching                     |    |

|      | condition is met                                                                               | 44 |

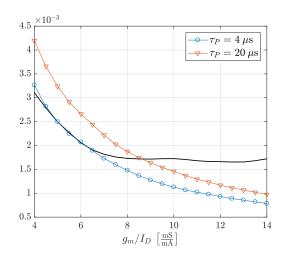

| 3.10 | Optimum condition for peaking time values of $\tau_P=4~\mu s$ and $\tau_P=20~\mu s$            | 45 |

| 3.11 | $F_o$ as a function of $I_D$ . The same parameters as in Figure 3.6 were considered,           |    |

|      | with the exception of $\tau_P$                                                                 | 46 |

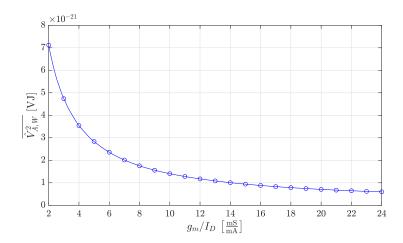

| 3.12 | Normalized amplifier white noise PSD $vs.$ $g_m/I_D$ . For strong inversion operation white noise is $\propto (g_m/I_D)^{-1}$ which is directly observable on the                                                                                                                                          |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | plot. This inverse relation with $g_m/I_D$ translates into diminishing returns in                                                                                                                                                                                                                          | 45 |

| 2.12 | noise performance with increasing values of $g_m/I_D$                                                                                                                                                                                                                                                      |    |

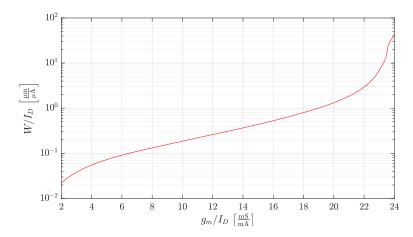

| 3.13 | Width per unit current $W/I_D$ , reciprocal of current density $I_D/W$                                                                                                                                                                                                                                     | 48 |

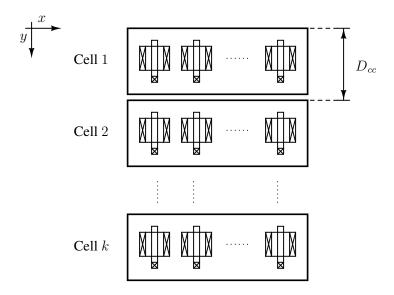

| 4.1  | Cell-based layout with horizontally aligned, vertically stacked cells                                                                                                                                                                                                                                      | 56 |

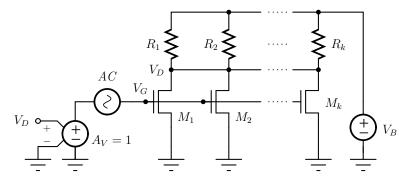

| 4.2  | Schematic for Monte Carlo mismatch simulations. A single equivalent device circuit is considered. Simulation parameters include $L_j=0.6\mu\mathrm{m},~W_j=127.5\mu\mathrm{m},~R_j=1\Omega,$ and $V_B=1\mathrm{V}.$ This bias voltage results in the device                                                |    |

|      | operating in strong inversion, at a $g_m/I_D \approx 4.5  \frac{\text{mS}}{\text{mA}}$                                                                                                                                                                                                                     | 64 |

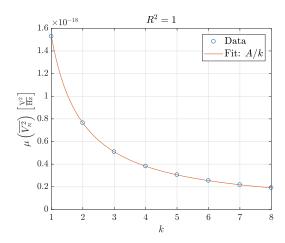

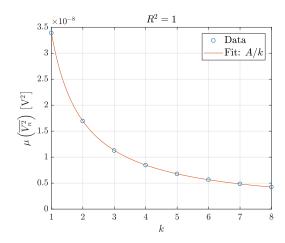

| 4.3  | Mean input-referred noise PSD $vs. \#$ of parallel connected cells. The results were obtained from simulation scenario $\#3$ , however, the resulting plots for the other simulation scenarios showed no measurable differences                                                                            | 66 |

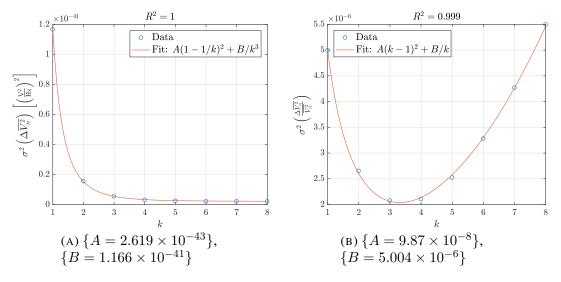

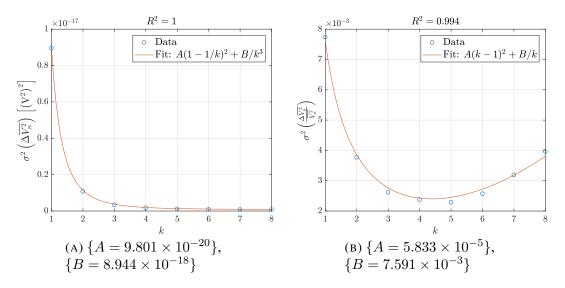

| 4.4  | Absolute (A) and normalized (B) variance of the input-referred noise PSD vs.                                                                                                                                                                                                                               |    |

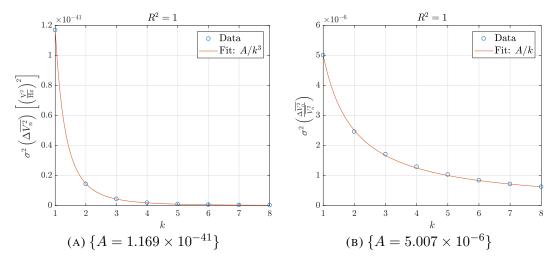

|      | # of parallel connected cells, for simulation scenario #1                                                                                                                                                                                                                                                  | 66 |

| 4.5  | Absolute (A) and normalized (B) variance of the input-referred noise PSD $vs$ . # of parallel connected cells, for simulation scenario #2                                                                                                                                                                  | 67 |

| 4.6  | Absolute (A) and normalized (B) variance of the input-referred noise PSD $vs$ . # of parallel connected cells, for simulation scenario #3                                                                                                                                                                  | 67 |

| 4.7  | Mean output integrated noise $vs. \#$ of parallel connected cells. The integrated bandwidth ranges from $0.1 \mathrm{\ mHz}$ to $100 \mathrm{\ kHz}$ . The results were obtained from simulation scenario $\#1$ . The resulting plots for the other simulation scenarios showed no observable differences. | 70 |

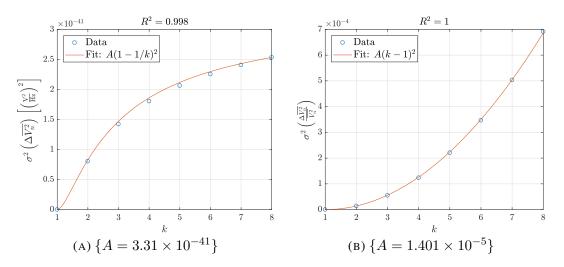

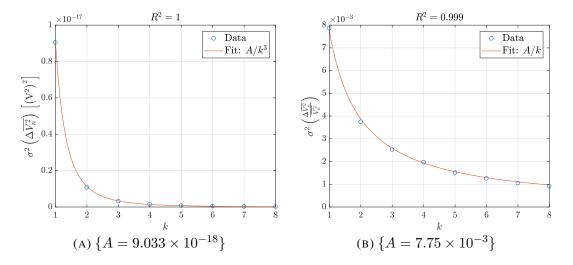

| 4.8  | Absolute (A) and normalized (B) variance of the output integrated noise $vs. \#$ of parallel connected cells, for simulation scenario $\#1. \ldots \ldots$                                                                                                                                                 | 70 |

| 4.9  | Absolute (A) and normalized (B) variance of the output integrated noise $vs. \#$ of parallel connected cells, for simulation scenario $\#2$                                                                                                                                                                | 71 |

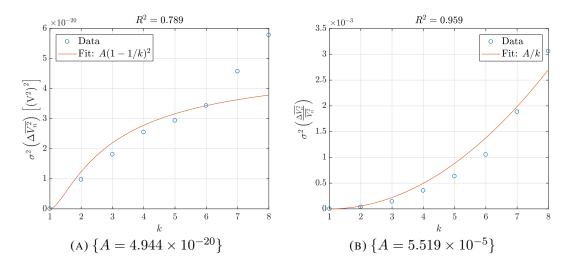

| 4.10 | Absolute (A) and normalized (B) variance of the output integrated noise $vs. \#$ of parallel connected cells, for simulation scenario $\#3. \ldots \ldots$ | 71 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

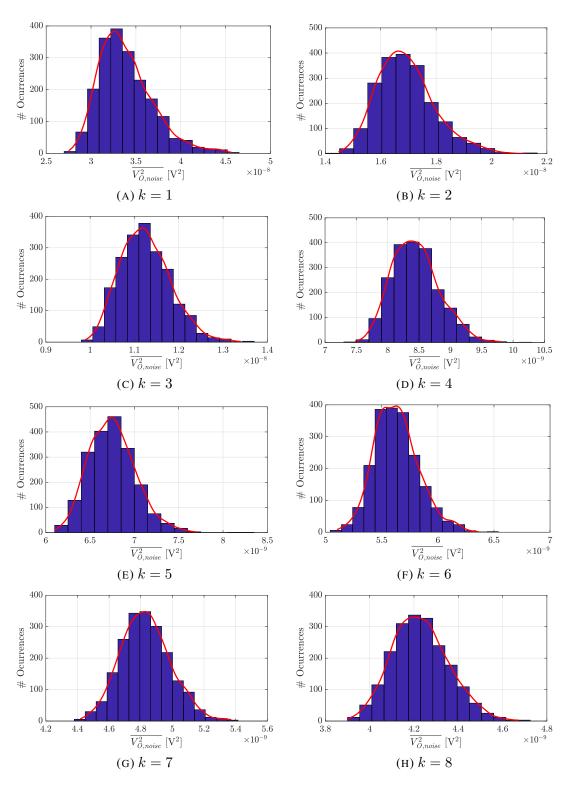

| 4.11 | Simulation scenario $\#1$ – Histogram of the output integrated noise for different                                                                         |    |

|      | numbers of parallel connected cells. A Kernel curve estimation of the probability                                                                          |    |

|      | density function is also included for each case, computed using the MATLAB                                                                                 |    |

|      | histfit command                                                                                                                                            | 74 |

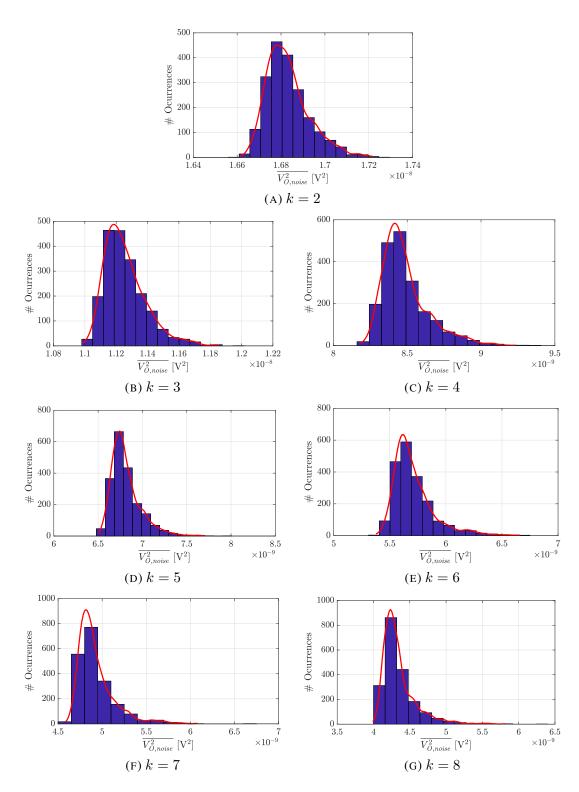

| 4.12 | Simulation scenario $\#2$ – Histogram of the output integrated noise for different                                                                         |    |

|      | numbers of parallel connected cells. A Kernel curve estimation of the probability                                                                          |    |

|      | density function is also included for each case. The histogram for $k=1\ \mathrm{was}$                                                                     |    |

|      | omitted, given that there is no dispersion in the noise measurements in that                                                                               |    |

|      | particular case                                                                                                                                            | 75 |

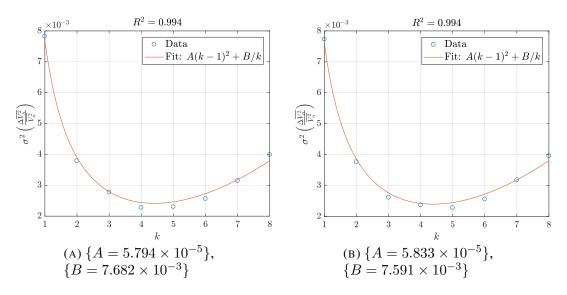

| 4.13 | CSA Monte Carlo simulation – Normalized variance comparison: switches (A)                                                                                  |    |

|      | vs. no switches (B)                                                                                                                                        | 76 |

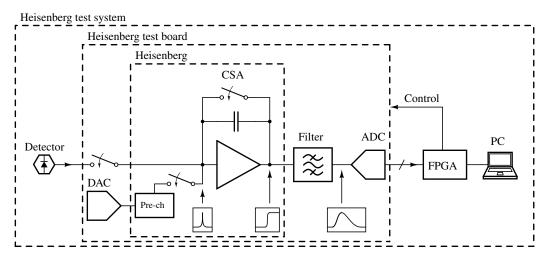

| 5.1  | Testing system block diagram.                                                                                                                              | 78 |

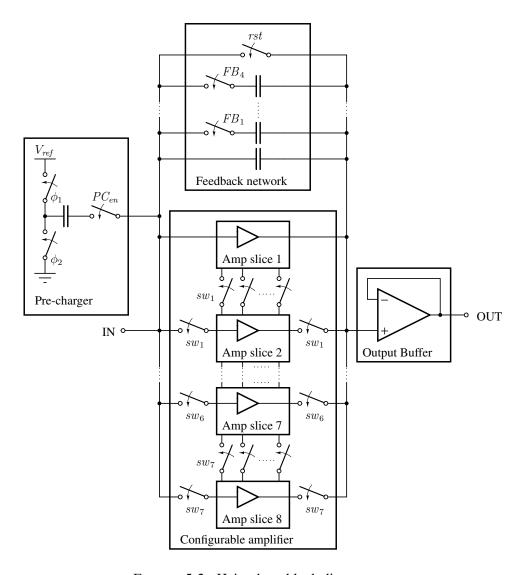

| 5.2  | Heisenberg block diagram.                                                                                                                                  | 79 |

| 6.1  | Generic CSA schematic for linearity analysis                                                                                                               | 82 |

| 6.2  | Schematic of a generic closed-loop CSA for frequency response analysis                                                                                     | 84 |

| 6.3  | Schematic of a NMOS-input folded-cascode amplifier                                                                                                         | 86 |

| 6.4  | Schematic of the folded-cascode amplifier for small-signal analysis                                                                                        | 87 |

| 6.5  | Schematic for the amplifier bias circuit                                                                                                                   | 90 |

| 6.6  | Parallel connection scheme                                                                                                                                 | 91 |

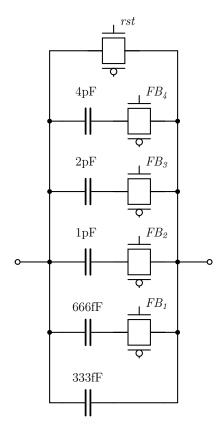

| 6.7  | Schematic for the feedback network                                                                                                                         | 92 |

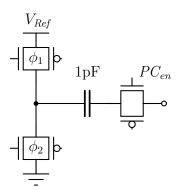

| 6.8  | Schematic for the pre-charger circuit                                                                                                                      | 93 |

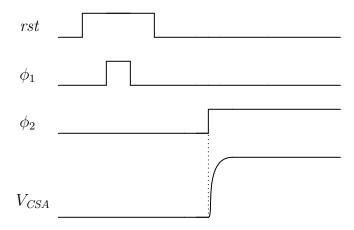

| 6.9  | Signal diagram for pre-charging and feedback reset                                                                                                         | 94 |

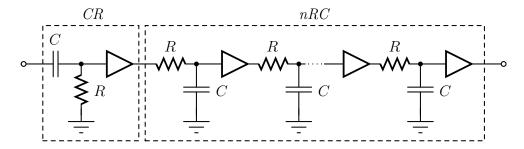

| 6.10 | Schematic of a generic $CR - nRC$ filter                                                                                                                   | 95 |

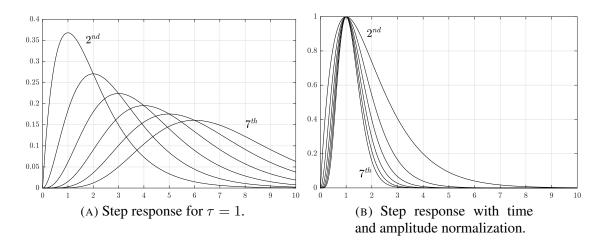

| 6.11 | Step response of a $CR - nRC$ filter for $n = \{1, 2,, 6\}$                                                                                                | 96 |

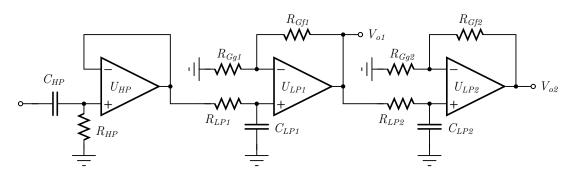

| 6.12 | Schematic of the filter in the Heisenberg test board                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------|

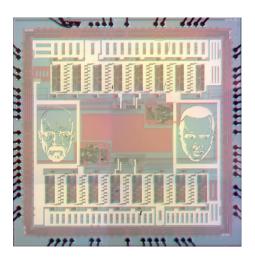

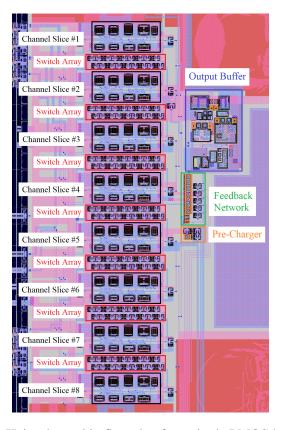

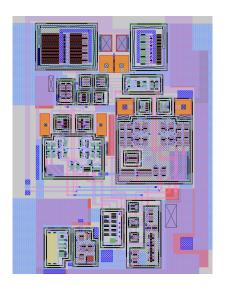

| 7.1  | Heisenberg chip micrograph                                                                                            |

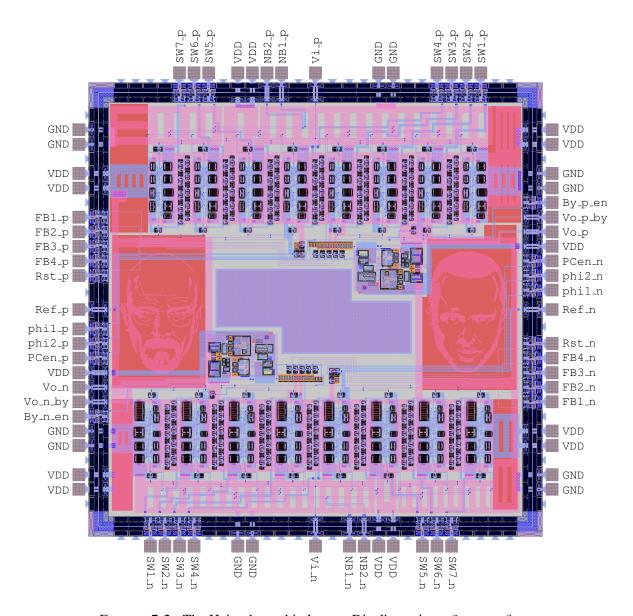

| 7.2  | The Heisenberg chip layout. Die dimensions: $3\text{-mm} \times 3\text{-mm}$                                          |

| 7.3  | Heisenberg chip floorplan for a single PMOS based channel                                                             |

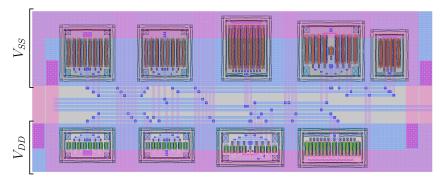

| 7.4  | Amplifier slice layout for both PMOS and NMOS input device designs 101                                                |

| 7.5  | Different approaches to slice stacking                                                                                |

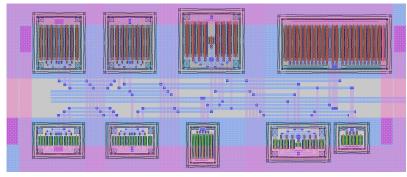

| 7.6  | Feedback network and pre-charger circuit layout                                                                       |

| 7.7  | Operational amplifier cell layout                                                                                     |

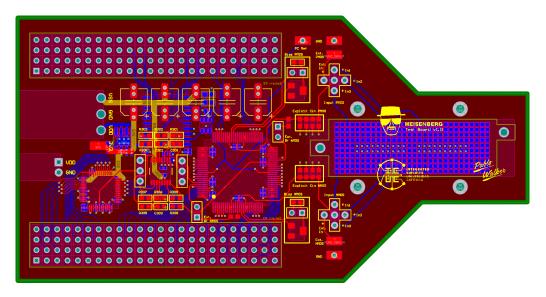

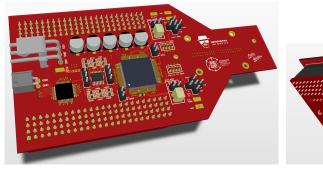

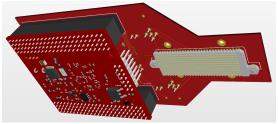

| 7.8  | Heisenberg test board. Dimensions: $124.9\text{-mm} \times 64.4\text{-mm}$ 104                                        |

| 7.9  | 3D model of the board stack between the Heisenberg test PCB and the FPGA                                              |

|      | board                                                                                                                 |

| 7.10 | Numato Saturn - Spartan-6 FPGA Development Board. Dimensions: $62.8 \text{mm} \times$                                 |

|      | 57.5mm                                                                                                                |

| 7.11 | Timing for the operation of the pre-charger circuit and data sampling. The                                            |

|      | timescale is distorted to better display the signal sequence                                                          |

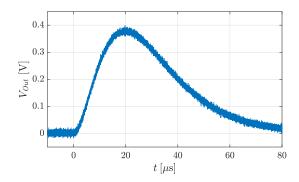

| 8.1  | Example of a noisy waveform ( $k=2, C_F=8 \text{ pF}$ )                                                               |

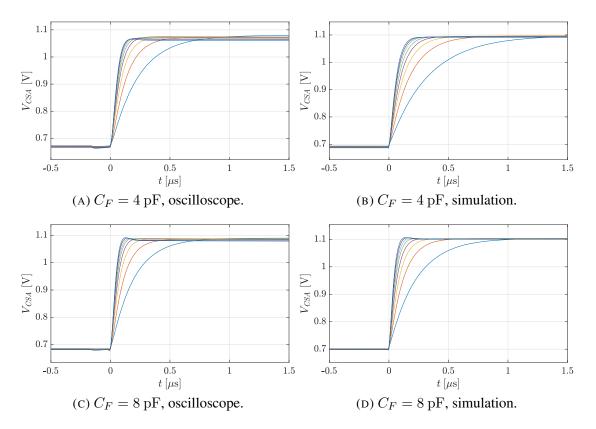

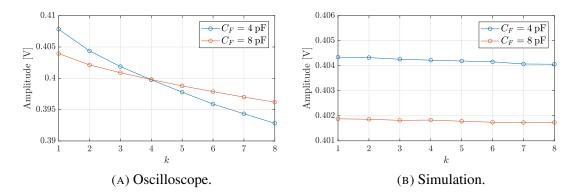

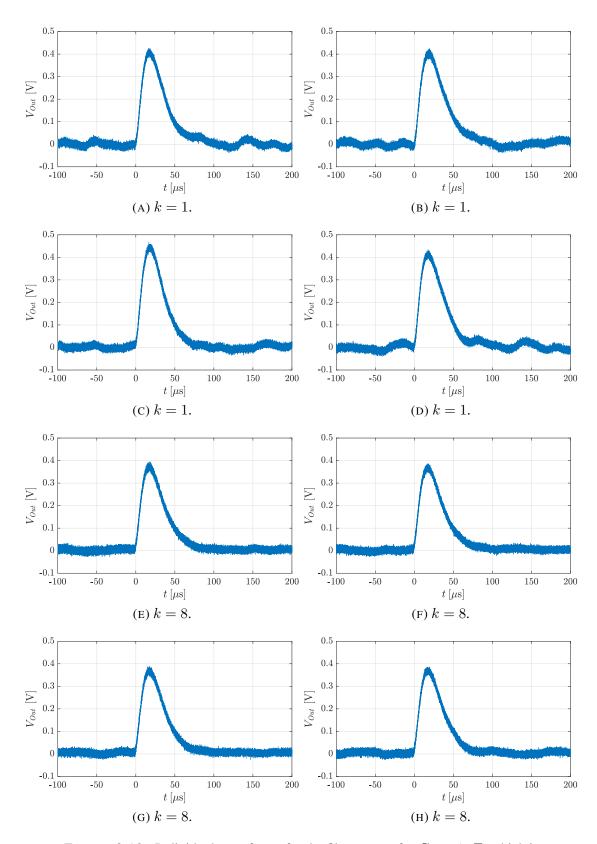

| 8.2  | Charge-sensitive amplifier output for different number of parallel-connected                                          |

|      | slices. Both measured waveforms and simulation waveforms are presented,                                               |

|      | for different values of $C_F$ . The measured waveforms were obtained using an                                         |

|      | oscilloscope, and averaging $8192$ identical events for each value of $k$ to remove                                   |

|      | noise. In all cases, there is a monotonic increase in signal bandwidth from the                                       |

|      | rightmost plot corresponding to $k=1$ , to the leftmost plot corresponding to                                         |

|      | $k = 8. \dots $ |

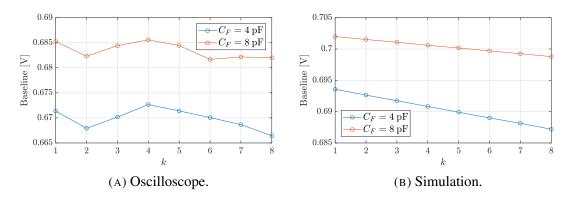

| 8.3  | Close-up of the baseline values just before the CSA step response                                                     |

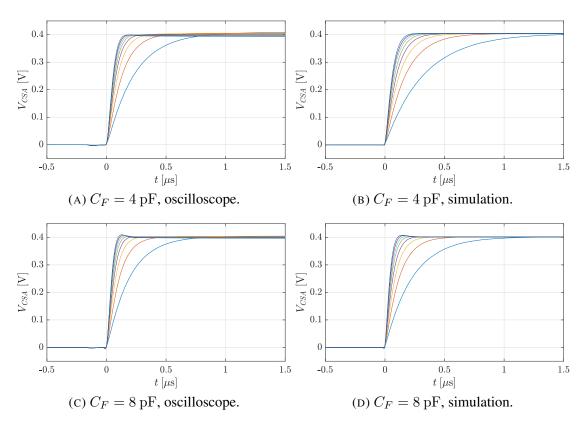

| 8.4  | Charge-sensitive amplifier output for different number of parallel-connected                                          |

|      | slices without baseline Both measured waveforms and simulation waveforms                                              |

|      | are presented, for different values of $C_F$ . In all cases, there is a monotonic                                             |

|------|-------------------------------------------------------------------------------------------------------------------------------|

|      | increase in signal bandwidth from the rightmost plot corresponding to $k=1$ , to                                              |

|      | the leftmost plot corresponding to $k = 8.$                                                                                   |

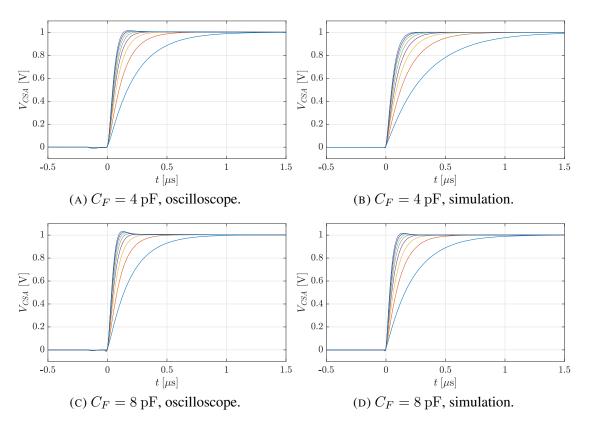

| 8.5  | Close-up of the amplitude values for the CSA step response. These values are                                                  |

|      | limited to the AC amplitude, and do not include the baseline. Furthermore,                                                    |

|      | these values were sampled when the waveform reached steady-state                                                              |

| 8.6  | Plot for $V(k) = Q_I/(C_F + k \cdot C_{FP})$ , where $Q_I$ and $C_{FP}$ were obtained through                                 |

|      | linear regression of the measured amplitude results. The estimated values are                                                 |

|      | $Q_I=1.635\mathrm{pC}$ and $21.34\mathrm{fF}$ for the $4\mathrm{pF}$ curve, and $Q_I=3.235\mathrm{pC}$ and $21.69\mathrm{fF}$ |

|      | for the 8 pF curve                                                                                                            |

| 8.7  | Charge-sensitive amplifier output for different number of parallel-connected                                                  |

|      | slices, without baseline and normalized to unit amplitude. Both measured                                                      |

|      | waveforms and simulation waveforms are presented, for different values of                                                     |

|      | $C_F$ . In all cases, there is a monotonic increase in signal bandwidth from the                                              |

|      | rightmost plot corresponding to $k=1$ , to the leftmost plot corresponding to                                                 |

|      | $k = 8. \dots $         |

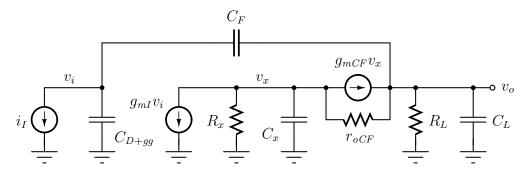

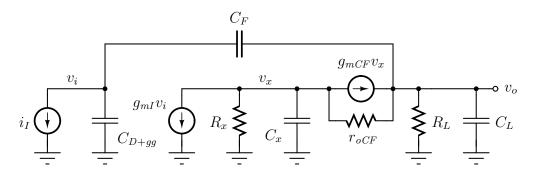

| 8.8  | Schematic of the NMOS-input folded-cascode amplifier for small-signal analysis,                                               |

|      | with capacitive feedback. An explicit capacitor to account for the non-dominant                                               |

|      | pole was added to the node $v_x$ to analyze the second-order response of the                                                  |

|      | circuit                                                                                                                       |

| 8.9  | CR - 2RC filter output for different number of parallel-connected slices. Both                                                |

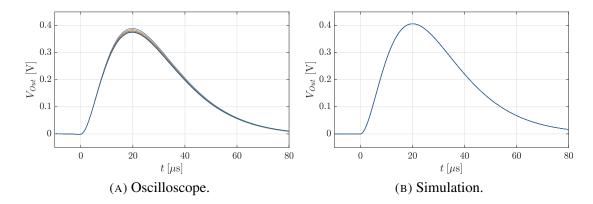

|      | measured waveforms and simulation waveforms are presented for $C_F=4~\mathrm{pF}.~125$                                        |

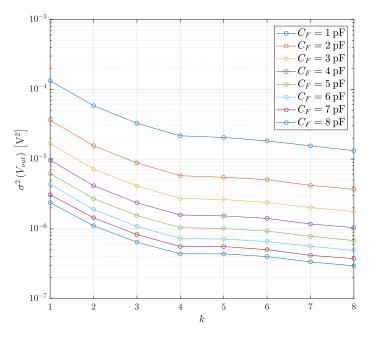

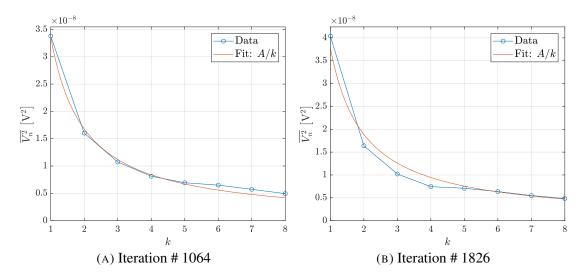

| 8.10 | Noise measurements for all the combinations of $k$ and $C_F$ used in the testing of                                           |

|      | the Heisenberg chip. The plot is presented with a logarithmic $y$ axis to be able                                             |

|      | to display all curves properly                                                                                                |

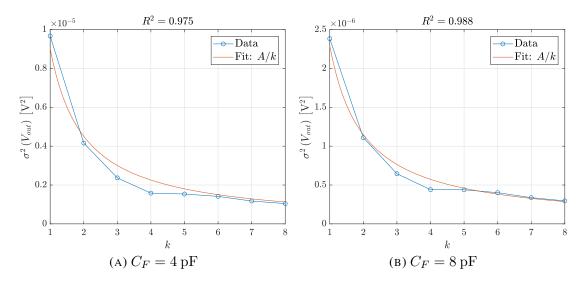

| 8.11 | Noise measurements for an increasing number of parallel-connected slices, and                                                 |

|      | two values of the feedback capacitance $C_F$ . A nonlinear least-squares fit is also                                          |

|      | included using the model for expected behavior ( $\propto 1/k$ )                                                              |

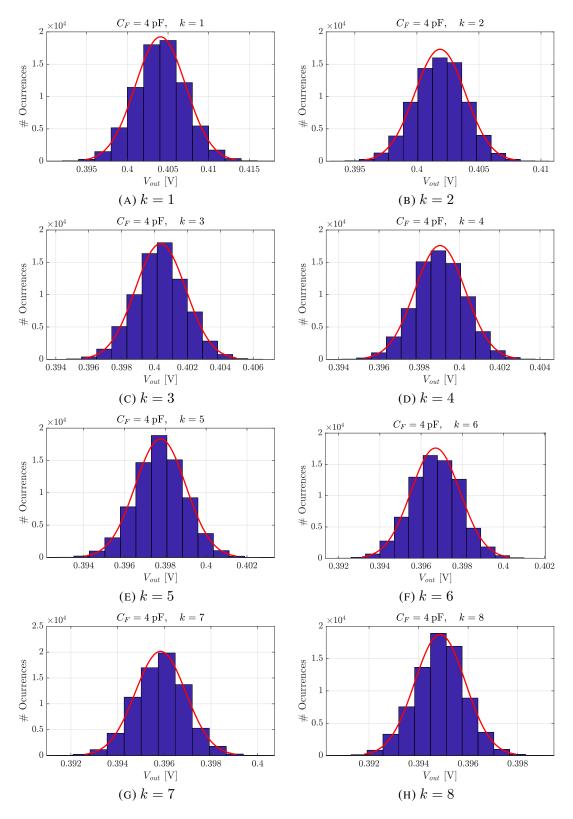

| 8.12 | Histograms for the filter output voltage, being sampled at the peaking time,                  |

|------|-----------------------------------------------------------------------------------------------|

|      | for different numbers of parallel-connected slices (k) using $C_F=4~\mathrm{pF}.$ The         |

|      | variance of each histogram represents the noise for that particular configuration             |

|      | of variables                                                                                  |

| 8.13 | Individual waveforms for the filter output for $C_F = 1 \text{ pF}$ , which is the smallest   |

|      | value available for the feedback capacitance on the Heisenberg chip. Two                      |

|      | different values of $k$ ( $k = 1$ and $k = 8$ ) are presented                                 |

| 8.14 | Handpicked iterations of the Monte Carlo simulation of the CSA ( $C_F = 8 \mathrm{pF}$ ). 134 |

| A.1  | Schematic of the NMOS-input folded-cascode amplifier for small-signal analysis,               |

|      | with capacitive feedback. An explicit capacitor to account for the non-dominant               |

|      | pole was added to the $\boldsymbol{v}_{x}$ node to analyze the second-order response of the   |

|      | circuit 147                                                                                   |

## LIST OF TABLES

| 2.1 | Normalized MOSFET noise equations (Alvarez, Avila, Campillo, Dragone, and Abusleme (2012))                                                                     | 20  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Some commonly adopted time-invariant filters and the corresponding $ENC$ noise coefficients. The ratio between the pulse width $(\tau_W)$ and the peaking time |     |

|     | $(\tau_P)$ is also reported. Flicker exponent $A_F=1$ was considered (De Geronimo and O'Connor (2005))                                                         | 34  |

| 3.2 | Normalized noise equations (Alvarez et al. (2012))                                                                                                             | 36  |

| 4.1 | Examples of process and electrical parameters                                                                                                                  | 52  |

| 4.2 | Single device Monte Carlo simulation – Random and gradient standard deviation                                                                                  |     |

|     | values                                                                                                                                                         | 65  |

| 4.3 | Charge-sensitive amplifier Monte Carlo simulation – Random and gradient                                                                                        |     |

|     | standard deviation values                                                                                                                                      | 68  |

| 5.1 | Specifications summary                                                                                                                                         | 81  |

| 6.1 | Transistor design parameters for the charge-sensitive amplifier circuit                                                                                        | 89  |

| 6.2 | Transistor design parameters for the amplifier bias circuit. The drain current for                                                                             |     |

|     | all transistors is $I_D=25~\mu\mathrm{A.}$                                                                                                                     | 90  |

| 6.3 | Filter parameter values                                                                                                                                        | 97  |

| 7.1 | FPGA digital I/Os.                                                                                                                                             | 106 |

| 7.2 | Timing parameters                                                                                                                                              | 107 |

| 8.1 | Parameters for noise calculations                                                                                                                              | 131 |

#### **ABSTRACT**

Advances over the last decades in electronic design automation (EDA) for the design of digital integrated circuits, have led to the development of a robust set of tools and methodologies that automate almost all low-level phases of the digital design workflow. In contrast, analog integrated circuit design remains a mostly handmade, time-consuming and knowledge-intensive process. The amount of design iterations can be heavily cut down by the use of realistic value tables through the  $g_m/I_D$  design technique; however, the process still remains time-consuming and error-prone, with an end result of limited applicability beyond the scope of the initial specifications.

The slice-based design methodology, first introduced in this thesis, is a new approach to analog integrated circuit design, suitable for implementation in EDA tools, that aims to help reduce the amount of time and expertise required from the user. This methodology, inspired by the  $g_m/I_D$  design technique, is based on the use of pre-designed circuit cells, which can be connected in parallel to scale important performance metrics.

This thesis serves as a practical exploration of the slice-based design methodology. Given the difficulty of assessing the applicability and practicality of the proposed design methodology to any arbitrary circuit topology, it was decided to limit the scope of the analysis to a particular target application: low-noise charge-sensitive amplifiers (CSA) used for instrumentation in particle physics experiments. Within this context, a custom application-specific integrated circuit (ASIC) was designed, fabricated and tested, which includes a CSA designed with the slice-based technique, to evaluate practical design considerations and measure real-world performance.

**Keywords:** Electronic design automation (EDA), Slice-based design, Particle physics instrumentation, Charge-sensitive amplifier (CSA), Electronic noise, Device mismatch

#### **RESUMEN**

Los avances durante las últimas décadas en la automatización del diseño electrónico (EDA) para el diseño de circuitos integrados digitales, han llevado al desarrollo de un conjunto de herramientas y metodologías robustas que automatizan casi todas las etapas de bajo nivel en el flujo de diseño digital. En contraste, el diseño de circuitos integrados analógicos sigue siendo un proceso hecho mayormente a mano, que requiere mucho tiempo y conocimientos. La cantidad de iteraciones de diseño puede reducirse con el uso de tablas de valores realistas mediante la técnica de diseño  $g_m/I_D$ , sin embargo, el proceso sigue siendo lento y propenso a errores, con un resultado final de aplicabilidad limitada más allá del alcance de las especificaciones iniciales.

La metodología de diseño basado en *slices*, introducida por primera vez en esta tesis, es un nuevo enfoque para el diseño de circuitos integrados analógicos, adecuado para la implementación en herramientas EDA, que tiene como objetivo ayudar a reducir la cantidad de tiempo y conocimiento requerido por el usuario. Esta metodología, inspirada en la técnica de diseño  $g_m/I_D$ , se basa en el uso de celdas de circuito pre-diseñadas, que pueden ser conectar en paralelo para escalar medidas de desempeño importantes.

Esta tesis sirve como una exploración práctica de la metodología de diseño basada en *slices*. Dada la dificultad de evaluar la aplicabilidad y practicalidad de la metodología de diseño propuesta a una topología de circuito arbitraria, se decidió limitar el alcance del análisis a una aplicación objetivo en particular: amplificadores sensibles a la carga (CSA) de bajo ruido utilizados en instrumentación para experimentos de física de partículas. En este contexto, un circuito integrado de aplicación específica (ASIC) *custom* fue diseñado, fabricado y probado, que incluye un CSA diseñado con la técnica basada en *slices*, para evaluar consideraciones prácticas de diseño y medir el desempeño real del circuito.

**Palabras Claves:** Automatización de diseño electrónico (EDA), Diseño basado en *slices*, Instrumentación para física de partículas, Amplificador sensible a la carga (CSA), Ruido electrónico, *Mismatch* en dispositivos

#### 1. INTRODUCTION

#### 1.1 Analog integrated circuit design

#### 1.1.1 The design process

The proliferation of consumer electronics has been a driving factor in the advancement of integrated circuit (IC) design towards increasingly complex circuits and ever smaller process technologies. The move towards design complexity has been aided by a mature and widely available set of tools for Electronic Design Automation (EDA) in the digital domain. To take advantage of these tools, circuit functions (*e.g.* signal processing) are implemented in the digital domain whenever possible. In stark contrast, analog IC design lacks the automation tools that facilitate the design process, and remains essentially hand-crafted by analog designers, on technologies typically optimized for digital applications. Due to this comparative disadvantage, on the design of systems on a chip (SoC)<sup>1</sup>, it is typically the development cycle of the analog blocks that bottleneck the design process, even though they comprise only a small area of the entirety of the chip (Martins, Lourenço, and Horta (2012)).

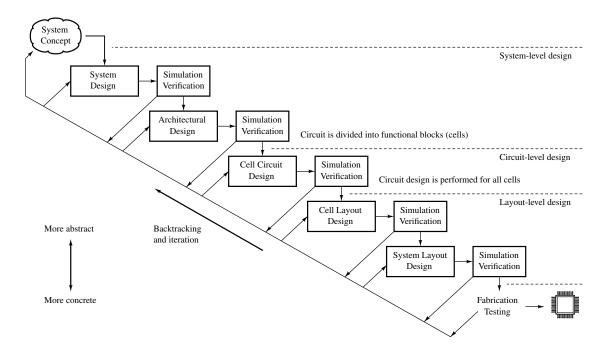

A typical electronic design flow for analog and mixed-signal integrated circuits is performed using a top-down approach, an example of which is shown graphically in Figure 1.1. Three levels of abstraction can be readily identified during the design process: the system-level, where system specifications are set and functional blocks are identified; the circuit level, where circuit schematics are designed for each functional block; and the layout-level, where the circuit layout for all the functional blocks is designed, followed by floorplanning, placement and global routing to generate the layout of the entire system. Simulation and verification steps are performed at each level to account for undesired effects (*e.g.* layout parasitics) and detect potential problems, and if the design fails to meet specifications at some point in the design flow, redesign iterations are performed.

<sup>&</sup>lt;sup>1</sup>An SoC may include analog, mixed-signals and digital blocks implemented on the same die

FIGURE 1.1. High-level view of the analog or mixed-signal design flow (Gielen and Rutenbar (2000)).

The circuit-level design is particularly challenging, as it often requires a custom optimized design, which is typically an underconstrained problem, with many degrees of freedom, and with many (often conflicting) performance requirements that must be taken into account (Gielen (2007)). To solve this problem effectively and produce an optimized design, an analog designer is required to have an advanced knowledge of device behavior, circuit topologies and design trade-offs. For these reasons, the analog design process is generally perceived to be less systematic, more heuristic, and much more knowledge-intensive than digital design (Gielen and Rutenbar (2000)).

#### **1.1.2** About systematization and automation

While EDA tools for analog design have not reached the level of maturity to be widely adopted, computer-aided design (CAD) tools have been fundamental to tackle the design flow for decades. An analog designer will routinely use circuit simulators (*e.g.* LTspice (Analog-Devices (1999))), layout editing environments (*e.g.* Virtuoso (Cadence (2006))) and verification tools (*e.g.* CALIBRE (Mentor (2006))) to reach an optimized design.

The absence of mature EDA tools for analog design is not due to lack of trying, as research into the topic has been going on since the mid-1980s. Three distinct hierarchical levels are identified in the literature for analog design automation (ADA) (Gielen and Rutenbar (2000)): topology selection, where the most appropriate circuit topology is selected based on the given specifications; specification translation, where high-level specifications are mapped into sub-blocks, and at the lowest level, into device sizes; and layout generation, the creation of the geometrical layout of the low-level sub-blocks and the place and route of these sub-blocks at a higher level. A thorough and comprehensive review of the literature and the state of the art of these topics can be found on (Barros, Guilherme, and Horta (2010)) for topology selection and specification translation, and on (Martins et al. (2012)) for layout generation.

At the circuit level, analog designers rely heavily on hand analysis and circuit simulators to derive low-entropy expressions (Middlebrook (1991)) suitable for design. Among the techniques that allow some degree of systematization to the process, the  $g_m/I_D$  technique stands out (Silveira, Flandre, and Jespers (1996), Flandre, Viviani, Eggermont, Gentinne, and Jespers (1997)). The technique relies on the use of  $g_m/I_D$  as a design variable, which is a measure of the level of inversion of a transistor, and the use of tables for  $g_m/I_D$ -dependent parameters built from precise simulation results, both of which contribute to a more insightful approach to the design process. A detailed explanation of the importance of the  $g_m/I_D$  ratio and the homonymous design methodology is presented in Section 1.6.

#### 1.2 Topics covered by the Thesis

The present thesis explores a technique for analog design, namely the slice-based design technique, suitable for implementation in EDA tools at the circuit and layout levels, but does not borrow concepts and techniques traditionally used in the literature of EDA, and was instead inspired in the  $g_m/I_D$  design technique.

In order to explore the proposed design technique and as a proof on concept, particle physics instrumentation was selected as the target application, and an integrated circuit,

namely the Heisenberg ASIC<sup>2</sup>, was designed, fabricated and tested. The Heisenberg chip prominently includes a charge-sensitive amplifier (CSA) with configurable performance, and the main metric used to test the circuit was noise performance.

#### 1.3 Particle physics experiments

Particle physics, also known as high-energy physics, is the field of natural science that studies the elementary particles that constitute matter, and the interactions between them (Nagashima (2013)). At the most fundamental level, that is, at the smallest scale, matter is constituted by a handful of different types of particles, replicated in astronomical quantities. Currently, the classification of all known elementary particles and their interactions is described by the Standard Model.

To peer deep into matter, particle physicist must first isolate elementary particles for study. Barring protons and electrons, isolated elementary particles do not occur naturally, but are instead created during high-energy collisions with other particles. There are three main particle sources that physicist use for experimentation: cosmic rays, nuclear reactors and particle accelerators (Griffiths (2008)).

In order to detect and measure the properties of elementary particles, particle physicist employ incredibly complex detector systems, in the context of large-scale experiments, which are among the most ambitious engineering projects mankind has ever built. A prime example of a type of particle physics experiments are particle colliders, the most prominent being the LHC<sup>3</sup> (Evans and Bryant (2008)), located at CERN<sup>4</sup>, on the outskirts of Geneva, Switzerland.

Particle colliders are comprised of a particle accelerator, a detector system and a data processing system. The accelerator increases the energy of two particle beams traveling in opposing directions, and focuses them on a collision point. The resulting debris is

<sup>&</sup>lt;sup>2</sup>Application-specific integrated circuit.

<sup>&</sup>lt;sup>3</sup>Large Hadron Collider.

<sup>&</sup>lt;sup>4</sup>European Organization for Nuclear Research.

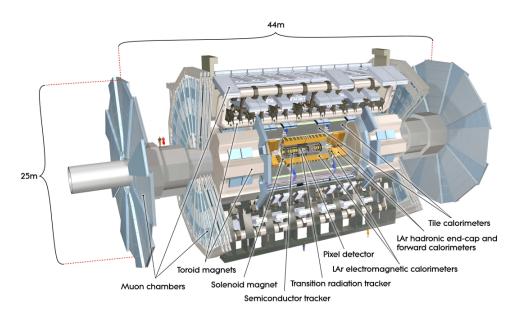

FIGURE 1.2. Cut-away view of the ATLAS detector (ATLAS Collaboration (2008)).

measured by the detector system, and the data stored for subsequent analysis. In modern particle accelerators, particles are made to collide at MHz rates during periods extending several months. The statistics of the large amount of accumulated data is then used to identify particles and measure their properties. An example of the results of particle physics experimental research is the recent of the Higgs Boson by the ATLAS (ATLAS Collaboration (2012)) and CMS (CMS Collaboration (2012)) experiments at the LHC.

Around the interaction point of a collider, a multi-layered detector system measures the collision debris, where each detector layer fulfills a different and specific purpose (*e.g.* particle tracking or calorimetry), with a multitude of individual detectors or detector channels on each layer. Figure 1.2 shows and example of one such detector system, the ATLAS detector (ATLAS Collaboration (2008)), centered at one of the collision points of the LHC.

As technology has advanced, and as particle physicist continue to pursue increasingly higher energies, the performance requirements of the individual detectors that comprise an experiment have grown ever more demanding. Modern finely segmented detectors can

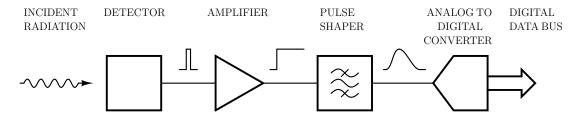

FIGURE 1.3. Block diagram for a single channel of a generic pulse processing circuit for particle physics experiments.

have hundreds of channels each, which are read by a handful of multichannel ASICs. Each one of these signal channels is read-out by an analog front-end, designed to comply with stringent speed, noise and power specifications.

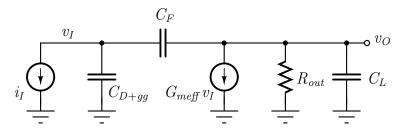

The results of the technological advancements brought about by particle physics research is not limited to scientific understanding. From the World Wide Web, to modern medical imaging (*e.g.* MRI, PET scan), to the touchscreen that everyday consumer electronics use, many modern technologies owe their origin to the technological advancements brought about by particle physics experimentation.

#### 1.4 Electronics for particle physics experiments

Although particle physics detector systems can take many different forms, their associated electronics perform the same basic functions (Grupen and Shwartz (2008)). The signal from the detector or detector channel in a multichannel array must be acquired, amplified, filtered and stored for subsequent analysis. A single channel of a generic particle physics detector system includes the detector, an amplifier, a filter, an analog-to-digital converter (ADC), and a readout circuit (Spieler (2005)). Figure 1.3 shows a simplified block diagram for a generic detector channel. A brief description of the function and operation of these functional blocks is presented below.

#### 1.4.1 Detector

The detector converts the energy deposited by the particle into an electrical signal, typically in the form of a finite amount of electrical charge proportional to the absorbed

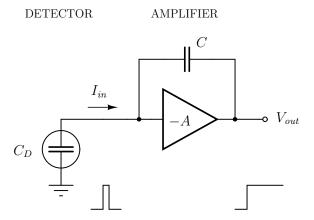

FIGURE 1.4. Front-end amplifier for particle physics instrumentation using a charge-sensitive amplifier. The charge generated by the detector is integrated on the feedback capacitor of the voltage amplifier to obtain a voltage step at the output.

energy. This can be achieved in a variety of ways, although the physical phenomena used for particle detection is out of the scope of this document. Common detector technologies include ionization chambers, scintillation counters, semiconductor detectors, and Cerenkov detectors, among others.

Detectors can also be classified according to their purpose, such as calorimeters and trackers. The former is used to measure the kinetic energy of particles by stopping the particle within its structure, the latter is used to detect particle trajectories, so they are typically highly segmented in order to obtain a good spatial resolution. More detailed information related to particle detectors can be found in (Grupen and Shwartz (2008)).

#### 1.4.2 Amplifier

The front-end amplifier, also known as preamplifier, translates the electrical charge generated by the detector into a voltage signal. The charge-to-voltage translation is done by transfering the charge  $Q_{in}$  from the nonlinear capacitance of the detector  $C_D$  to a known capacitor C. The output voltage  $V_{out}$  of the amplifier is given by  $V_{out} = Q_{in}/C$ , and the gain of the amplifier is naturally measured in [V/C] or  $[F^{-1}]$ . The most common preamplifier implementation consists of a voltage amplifier with a capacitor in negative

FIGURE 1.5. Pulse shaping action done by the filter. The filter sets the peaking time  $\tau_P$ , which in turn sets the conflicting requirements of noise bandwidth and system speed.

feedback configuration, as shown in Figure 1.4. The resulting feedback circuit is a charge-sensitive amplifier (CSA), which has been extensively studied in the literature related to particle physics instrumentation (Snoeys et al. (2000), Aspell et al. (2001), De Geronimo and O'Connor (2005), O'Connor and De Geronimo (1999), Alvarez et al. (2012)).

#### 1.4.3 Pulse Shaper

The primary function of the pulse shaper is to improve the signal-to-noise ratio (SNR). The frequency spectra of the signal and the noise differ, so it is possible to improve the SNR by applying a filter that tailors the frequency response to favor the signal, while attenuating the noise (Spieler (2005)). The filter also changes the time response of the input signal, as shown in Figure 1.5, reason why this functional block is referred to as pulse shaper. In this context, the terms pulse shaper and filter are used interchangeably.

The pulse shaper is typically an analog block, either time-invariant or time-varying, which sets both the speed and the total noise of the output signal before digitization. When designing a particle physics instrumentation system, it is necessary to find a balance between these two conflicting requirements.

#### 1.4.4 Digitizer

The output of the pulse shaper is sampled at the peak value of the pulse shape and digitized using an analog-to-digital converter (ADC). On highly segmented multichannel detectors, the ADC is typically included on the front-end ASIC, and can be either dedicated or shared among multiple channels.

#### 1.5 Noise in electronics

Noise is a generic term used to refer to any and all unwanted disturbances on a physical process. In electronics, noise is a current or voltage that is unwanted on an electrical circuit (Baker (2010)), which in turn manifests as unwanted disturbances on the desired signals of the circuit. Electronic noise sets the lower amplitude bound for the achievable resolution of a circuit, below which signal and noise are indistinguishable.

Types of noise can be broadly categorized as 1) electronic noise, which is the result of the discrete and random movement of electrical charge on an electrical device (*e.g.* thermal noise, shot noise, or flicker noise), 2) quantization noise, resulting from analog to digital domain conversions and vice versa, due to the discrete nature of digital signals, and 3) common-mode noise, resulting from extrinsic signals being picked up by the circuit and interfering with the desired signal.

Electronic noise is of particular importance to an analog circuit designer, and the main focus of the present document, since it is a direct consequence of the low level circuit design, unlike quantization noise and common-mode noise, which can be attributed to system level specifications (*e.g.* ADC resolution), and layout and implementation considerations (*e.g.* bad layout practices, poor EMI<sup>5</sup> shielding), respectively.

In integrated circuits, semiconductor devices (e.g. diodes, bipolar and MOS transistors) and resistors are the main sources of noise. A proper understanding of the underlying noise generating processes of MOS transistors is necessary for the design of low noise analog circuits in CMOS technologies. There are three uncorrelated noise generating processes in MOSFETs (Gray, Hurst, Lewis, and Meyer (2001)): 1) shot noise due to gate leakage current, 2) channel noise, which is a combination of thermal noise in strong inversion levels and shot noise in weak inversion levels, 3) and flicker or 1/f noise, also known as low-frequency noise. For moderate inversion levels, channel noise is modeled as a weighted average of both thermal and shot noise sources.

<sup>&</sup>lt;sup>5</sup>Electromagnetic Interference.

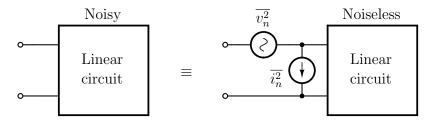

FIGURE 1.6. Equivalent representation of a noisy linear circuit as a noiseless linear circuit with external noise generators, referred to a single arbitrary port.

Since electronic noise is modeled as a stationary stochastic process, it is naturally characterized by its power spectral density (PSD), measured in  $[V^2/Hz]$  or  $[A^2/Hz]$ . The integral of the PSD over the circuits bandwidth yields the total noise power, and its square root is the standard deviation or RMS<sup>6</sup> value of the voltage or current noise.

Any linear circuit with noisy components can be represented as an ideal noiseless linear circuit with external noise generators (Gray et al. (2001)). This situation is shown in Figure 1.6. These noise generators are characterized by their power spectral densities  $\overline{v_n^2}(f)$  and  $\overline{i_n^2}(f)$ . Referring a noise source to one of the ports of a circuit is done by using the transfer function between the two.

For a fair comparison between the contribution of different noise sources on the same circuit, between the accumulated noise and the input signal, and even between different circuit topologies, is it often a good idea to refer the noise sources to the input port. When multiple noise sources are referred to the same port, the superposition of the noise contributions is applied in quadrature, considering correlation, as follows:

$$\sigma_{Tot}^2 = \sum_{i=1}^N \sigma_i^2 + \sum_{i \neq j} c_{ij} \cdot \sigma_i \cdot \sigma_j$$

(1.1)

where  $\sigma_i^2$  represents the noise power of source i, N is the total number of noise sources, and  $c_{ij}$  is the correlation coefficient between sources i and j. The total noise of the circuit on a given port is the integral over frequency of all port-referred contributions.

<sup>&</sup>lt;sup>6</sup>Root mean square.

#### **1.6** The $g_m/I_D$ design methodology

As CMOS technology has advanced, the behavior of the MOS transistor has changed enormously due to scaling and ever smaller operating voltages, making square-law equations obsolete (Razavi (2001)). In parallel, increasingly complex MOSFET models have been developed, *e.g.* the BSIM3 MOSFET model (Liu et al. (1998)), which accurately describe transistor behavior from weak to strong channel inversion, at the expense of complexity.

Design in moderate inversion, which is arguably the most complicated operating region to model, is increasingly important in modern, low voltage processes, due to high transconductance efficiency traded at a reasonable cost in bandwidth. In order for the analog designer to detach from overly complex low-level I-V transfer curves impractical for design, the  $g_m/I_D$  design methodology relies on the results of SPICE simulations, which are based on very accurate device models. Furthermore, the methodology employs the use of the inversion level of a transistor as a design variable, which leads to a more insightful approach to the design process. In this section, the importance of the  $g_m/I_D$  ratio and the basics of the design methodology of the same name are presented.

#### **1.6.1** The $g_m/I_D$ ratio as a design variable

Analog CMOS design is complicated by three degrees of design freedom present for every MOS device operating in the usual saturation region (Binkley (2007)). Traditionally, these design variables have been the drain current  $I_D$ , channel width W, and channel length L. However, selecting drain current, level of inversion, and channel length, provides better insight into device operation leading to a more optimized design, where channel width can be readily calculated as a consequence of these three design variables.

Among the figures of merit defined to quantify the level of inversion of MOS devices, the inversion coefficient IC (Vittoz (1994), Foty, Bucher, and Binkley (2002)), and the ratio between the transconductance  $g_m$  and the DC drain current  $I_D$ , hereafter referred to simply as  $g_m/I_D$  (Silveira et al. (1996), Flandre et al. (1997)), stand out. The latter will

be used for the remainder of the present document, and will serve as a design variable in the  $g_m/I_D$  design methodology.

The choice of  $g_m/I_D$  as a design variable is based on its relevance for three reasons:

- 1. It is directly related to the performance of MOS devices.

- 2. It provides an indication of the inversion level.

- 3. It can be used to calculate the dimensions of the transistor.

The first of these points is immediately apparent, as the  $g_m/I_D$  value is a measure of the efficiency to translate current into transconductance: if the transistor possesses a high  $g_m/I_D$  ratio, it means that it produces a large  $g_m$  per unit current. The unit for  $g_m/I_D$  is [1/V], or equivalently, [mS/mA].

To better understand what information about the level of inversion of a device is provided by the  $g_m/I_D$  ratio, let us consider the following relation:

$$\frac{g_m}{I_D} = \frac{1}{I_D} \cdot \frac{\partial I_D}{\partial V_{GS}} = \frac{\partial \left[\ln(I_D)\right]}{\partial V_{GS}} = \frac{\partial \left\{\ln\left[\frac{I_D}{\left(\frac{W}{L}\right)}\right]\right\}}{\partial V_{GS}}$$

(1.2)

In weak inversion, or subthreshold region, MOS devices behave as bipolar transistors (Gray et al. (2001)), and the dependence of the drain current  $I_D$  with the gate-to-source voltage  $V_{GS}$  is exponential. This means that the relationship between  $\ln(I_D)$  and  $V_{GS}$  is linear, and the derivative is constant. This constant value is where the derivative (1.2) is maximized, and this maximum value is equal to  $1/(nU_T)$ , where n is the subthreshold slope factor, which is technology dependent, and  $U_T$  is the thermal voltage. As the  $g_m/I_D$  value decreases, the operating point moves towards strong inversion, or active region, where the dependence of  $I_D$  and  $V_{GS}$  is quadratic, which means that  $\frac{\partial [\ln(I_D)]}{\partial V_{GS}} \propto \frac{1}{V_{GS}}$ . Deeply into strong inversion, the relation between  $I_D$  and  $V_{GS}$  becomes almost linear due to velocity saturation (Silveira et al. (1996)).

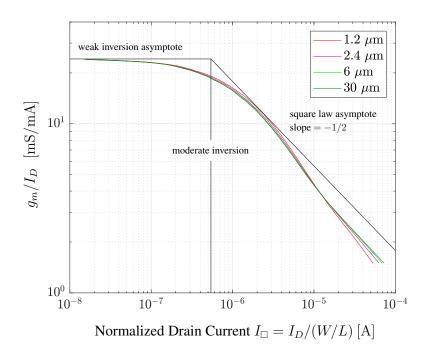

The previously stated observations are better illustrated via a simple but powerful graphical method shown in Figure 1.7 (Foty et al. (2002)), where the  $g_m/I_D$  ratio is plotted against the normalized drain current  $I_{\Box}=I_D/(W/L)$ , for a 0.5- $\mu$ m technology. The

FIGURE 1.7.  $g_m/I_D$  vs. normalized drain current  $I_{\square}$  for different values of L on a 0.5- $\mu$ m technology. Data points obtained from LTspice simulations using BSIM3 MOSFET models.

simple limits of device behavior are shown as two asymptotes: the weak inversion asymptote, where  $g_m/I_D$  approaches the thermal voltage limit for transconductance efficiency, and the strong inversion asymptote, which illustrates the traditional square-law MOSFET model, in the form of a line plot with a slope of -1/2. Centered at the point where these two asymptotes intersect, lies the interpolation region of moderate inversion, which extends as a continuum between these two regions of operation.

#### 1.6.2 Methodology

The basics of the  $g_m/I_D$  methodology are simple. Let us consider a transistor of width W and length L biased at a certain operating point, with a gate-to-source voltage  $V_{GS}$ , drain current  $I_D$ , transconductance  $g_m$ , and gate-to-source capacitance  $C_{gs}$ . If an identical transistor is connected in parallel, the equivalent device will have a width of  $2 \cdot W$ , drain current of  $2 \cdot I_D$ , transconductance of  $2 \cdot g_m$ , gate-to-source capacitance of  $2 \cdot C_{gs}$ , while the length L, the gate-to-source voltage  $V_{GS}$ , and the ratio  $g_m/I_D$ , a measure of the level

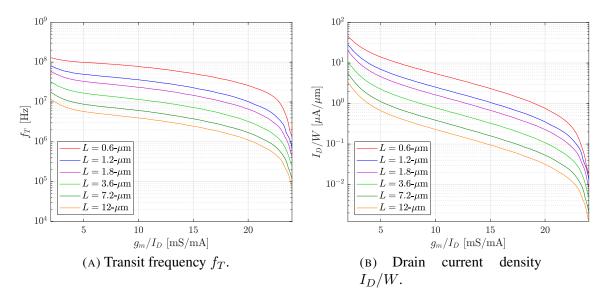

FIGURE 1.8. Relevant design ratios v.s.  $g_m/I_D$  for different values of L on a 0.5- $\mu$ m technology. Data points obtained from LTSpice simulations using BSIM3 MOSFET models

of inversion of the channel, remain unchanged. There are several other ratios that are only dependent on the operating point of the transistor, independent of device width, including the transit frequency  $f_T$  (commonly defined as  $g_m/C_{gs}$ ), drain current density  $I_D/W$ , and even normalized noise  $\overline{I_n^2}/I_D$  (Alvarez and Abusleme (2012)).

The  $g_m/I_D$  methodology requires device characterization prior to the design stage, in a process that needs to be performed only once for a given technology. Through SPICE simulations, value tables for width-independent parameters can be computed and mapped as a function of  $g_m/I_D$ , for different values of L. Furthermore, value tables for parameters that are also a function of the drain-to-source voltage  $V_{DS}$ , such as the intrinsic gain of the transistor  $g_m r_o$ , can also be computed by adding another simulation axis for  $V_{DS}$ . After the simulations have been carried out and the values stored, interpolation functions in a numerical-analysis software (e.g. MATLAB, SciLab, Excel) can be used to retrieve specific values as a function of  $g_m/I_D$  and L. Figure 1.8 shows  $g_m/I_D$  curves for the drain current density  $I_D/W$  and transit frequency  $g_m/C_{gs}$  of a 0.5- $\mu$ m technology, obtained from LTspice simulations while using BSIM3 MOSFET models. It can be inferred from

the drain current density plot  $I_D/W$  that, once  $I_D$ ,  $g_m/I_D$  and L have been selected, the transistor width W can be calculated unambiguously.

With technology-specific value tables on hand, the design process can begin. The process involves the use of the three device design variables previously stated  $(I_D, g_m/I_D)$  and  $(I_D, g_m/I_D)$  and  $(I_D, g_m/I_D)$  are the process involves the use of the three device design variables previously stated  $(I_D, g_m/I_D)$  and  $(I_D, g_m/I_D)$  and  $(I_D, g_m/I_D)$  are the process involves the use of the three device design variables previously stated  $(I_D, g_m/I_D)$  and  $(I_D, g_m/I_D)$  are the process can begin. The process involves the use of the three device design variables previously stated  $(I_D, g_m/I_D)$  and  $(I_D, g_m/I_D)$  and  $(I_D, g_m/I_D)$  are the process involves the use of the three device design variables previously stated  $(I_D, g_m/I_D)$  and  $(I_D, g_m/I_D)$  are the process involves the use of the three device design variables previously stated  $(I_D, g_m/I_D)$  and  $(I_D, g_m/I_D)$  are the process involves the use of the three device design variables previously stated  $(I_D, g_m/I_D)$  and  $(I_D, g_m/I_D)$  are the process involves the use of the three device design variables previously stated  $(I_D, g_m/I_D)$  and  $(I_D, g_m/I_D)$  are the use of the u

#### 1.7 Thesis content

Chapter 2 provides an overview of the proposed slice-based design methodology for analog circuits, including the basic formulation, some specific examples, and an exploration of potential problems. Chapter 3 provides an in-depth look into the mathematical framework used in noise analysis of particle physics front-ends and the application of this framework to the specific problem of slice-based design, and also includes some novel ideas regarding flicker noise modeling using a  $g_m/I_D$  approach. Chapter 4 provides and analysis of the effects of device mismatch on the application of the proposed design methodology, in the form of both a mathematical model for mismatch as a function of a discrete number of parallel-connected circuit copies, and a Monte Carlo simulation to check the applicability of the model. In Chapter 5, the ASIC system-level design and specifications are presented. Chapter 6 shows the the circuit-level design of the ASIC, with a particular emphasis on the design of a single charge-sensitive amplifier cell and parallel connection scheme. Chapter 7 presents the layout-level implementation of the designed ASIC, together with the implementation of the test PCB and FPGA firmware. In Chapter 8, the test results are presented, and the potential implications of these results on the proposed design methodology are analyzed. Finally, Chapter 9 summarizes the results and contributions of this work, and presents ideas for future research.

#### 2. SLICE-BASED DESIGN METHODOLOGY

#### 2.1 Introduction

The inherent difficulties of the analog design process were presented in Section 1.1, and can be summarized as follows: despite great advances in EDA tools for digital design in the last decades, analog design remains a mostly handmade, time-consuming and knowledge-intensive process. The amount of design iterations can be heavily cut down by the use of realistic value tables through the  $g_m/I_D$  design technique, however, the process still remains time-consuming and error-prone, with an end result of limited applicability beyond the scope of the initial specifications.

The slice-based design methodology, object of study of the present thesis, aims to help reduce the amount of time and manual work required from the user, while at the same time lowering the barrier of entry to non-experts in the design analog integrated circuits. From the perspective of the user, the methodology involves the use of a library of optimized circuits to cover different corners of the design space. The circuits in this library are indivisible cells, hereafter referred to as slices, that can be connected in parallel in order to scale important performance metrics. Through the careful selection of the correct slice and number of parallel-connected circuits, a wide range of specifications can be met with minimal time investment from the user. Thus, the design of a library of optimized and fully characterized circuit slices is a precondition for this methodology to be of any use.

As it is hard to say whether this methodology will be usable or appropriate in any arbitrary application, it was decided to limit the scope of the present research to amplifiers, and more specifically, to charge-sensitive amplifiers used in particle physics instrumentation. The applicability of the proposed design methodology to other types of circuits and applications is left for future research.

The present chapter provides a detailed description of the proposed design methodology, and can be broadly divided into two sections: Section 2.2 explores the effects of connecting large circuits blocks in parallel, and Section 2.3 presents the methodology, its

FIGURE 2.1. Illustration of the parallel connection of identical copies of a circuit.

implications at the circuit and layout levels, and potential problems with this approach to design.

#### 2.2 The effects of connecting circuits in parallel

The basis of the slice-based design technique is in the parallel connection of complex circuit blocks, in order to meet load, noise and other relevant specifications that scale with parallel connection, at the expense of power consumption and die area. The idea of connecting circuits in parallel to increase drive capability, or the trade-off between power consumption and noise performance, are not new concepts in IC design (Harris et al. (1999), Razavi (2001)), however, the idea of connecting large and complex circuits in parallel in order to scale circuit performance as an approach to the design process has not been found on the literature.

#### 2.2.1 The general case

When an arbitrary linear circuit (namely, circuit A) is connected in parallel to an identical copy of itself, *i.e.* each of the N nodes of the circuit is connected to the corresponding node of the identical copy, in the resulting circuit (namely, circuit B) some figures of merit and quantities change, whereas other stay the same. The concept is illustrated in Figure 2.1. For example, all the N node voltages remain, whereas all M branch currents are doubled:

$$v_{iB} = v_{iA} (2.1)$$

$$i_{jB} = 2i_{jA} (2.2)$$

As a consequence of this, all impedance elements  $Z_k$  are halved whereas all admittance elements  $Y_k$  are doubled. The latter includes transconductances as well:

$$Z_{kB} = \frac{Z_{kA}}{2} \tag{2.3}$$

$$Y_{kB} = 2Y_{kA} \tag{2.4}$$

This applies to both explicit passive elements (e.g. resistors, capacitors and inductors) and equivalent node impedances. Naturally, with the doubling of branch currents, power consumption is doubled as well. The operating point of all MOS devices stays the same, as the  $g_m/I_D$  ratio remains unchanged.

### 2.2.2 Single-pole amplifier

Some specific circuit blocks are also simple to analyze, such as an amplifier. Let us consider a single-pole amplifier with an open-loop gain of  $A_{OL}$  and a bandwidth of  $\omega_c$ . The open-loop gain of the amplifier, which is a non-dimensional figure, can be expressed as the product of the circuit effective transconductance  $G_{meff}$  and the output resistance  $R_{Out}$ . On the parallel connection of identical circuits, the former increases and the latter decreases, while the open-loop gain remains constant:

$$A_B = G_{meffB} \cdot R_{OutB} = 2G_{meffA} \cdot \frac{R_{outA}}{2} = A_A$$

(2.5)

The same is true for the bandwidth of the amplifier. The equivalent capacitance of the dominant pole increases twofold, while the equivalent resistance seen by the capacitor decreases by the same quantity:

$$\omega_{cB} = \frac{1}{R_{eqB} \cdot C_{eqB}} = \frac{1}{\frac{R_{eqA}}{2} \cdot 2C_{eqA}} = \omega_{cA}$$

(2.6)

However, it is not uncommon for the bandwidth of a circuit to be set by an externally connected load. As long as the load is also parallel-connected, the bandwidth is maintained, otherwise the bandwidth would change. Nonetheless, the resulting parallel-connected amplifier has twice the drive capability of the single circuit.

### 2.2.3 Noise analysis

In terms of noise, the effects of connecting circuits in parallel are more involved. Let us consider an arbitrary linear circuit that has a single noise generator. The simplest example is a resistor, which generates thermal noise. The power spectral density (PSD) of the thermal noise generated by a resistor is directly proportional to its resistance when expressed as a voltage variance, whereas when expressed as a current variance, it is inversely proportional to its resistance: