# PONTIFICIA UNIVERSIDAD CATOLICA DE CHILE SCHOOL OF ENGINEERING

# FERROELECTRIC MEMORY AND ARCHITECTURE FOR DEEP NEURAL NETWORK TRAINING IN RESISTIVE CROSSBAR ARRAYS

# CRISTÓBAL ALESSANDRI AMENÁBAR

Thesis submitted to Pontificia Universidad Católica de Chile and University of Notre Dame in partial fulfillment of the requirements for the Degree of Doctor in Engineering Sciences

Advisor:

ÁNGEL ABUSLEME CHRISTIAN GUZMÁN ALAN SEABAUGH

Santiago de Chile, April, 2019

© MMXIX, Cristóbal Alessandri Amenábar

# PONTIFICIA UNIVERSIDAD CATOLICA DE CHILE SCHOOL OF ENGINEERING

# FERROELECTRIC MEMORY AND ARCHITECTURE FOR DEEP NEURAL NETWORK TRAINING IN RESISTIVE CROSSBAR ARRAYS

# CRISTÓBAL ALESSANDRI AMENÁBAR

Members of the Committee:

**ÁNGEL ABUSLEME**

CHRISTIAN GUZMÁN

**ALAN SEABAUGH**

**CHRISTIAN OBERLI**

**PATRICK FAY**

SIDDHARTH JOSHI

JUAN DE DIOS ORTÚZAR

Thesis submitted to Pontificia Universidad Católica de Chile and University of Notre Dame in partial fulfillment of the requirements for the Degree of Doctor in Engineering Sciences

Santiago de Chile, April, 2019

$To\ Antonia$

## ACKNOWLEDGMENTS

I would like to thank my advisors Professor Alan Seabaugh, Professor Ángel Abusleme and Professor Dani Guzmán for their guidance and support throughout this thesis work. Special thanks to Ángel for introducing me to academic research and motivating me to pursue a PhD degree, and to Alan for giving me the advice, tools and freedom to successfully explore and develop my research path.

I would also like to thank Professors Siddharth Joshi, Patrick Fay, Suman Datta, Sharon Hu, Christian Oberli, Jaime Anguita and Marcelo Guarini for their support, insightful discussions and feedback throughout my PhD. I also thank Arman Kazemi, Sara Fathipour, Erich Kinder, Mina Asghari, Karla Gonzalez, Paolo Paletti, Enrique Álvarez, Diego Ávila and Matías Jara for many collaborations and discussions throughout these years. Special thanks to Pratyush Pandey, with whom I share many of the achievements presented in this thesis.

I also thank my parents for giving me an education and everything I ever needed to succeed. Last but not least, I thank my wife Antonia for selflessly joining me in this adventure and for her constant support.

This work was supported in part by the Center for Low Energy Systems Technology (LEAST), one of six centers of STARnet, a Semiconductor Research Corporation program sponsored by MARCO and DARPA, by the National Science Foundations NSF-DMR-EPM under grant No. 1607935, by CONICYT-PCHA/Doctorado Nacional/2014-2114059, by CONICYT-FONDECYT project 1130334 and by the Notre Dame Center for Research Computing.

#### ABSTRACT

Deep neural networks (DNN) can perform cognitive tasks such as speech recognition and object detection with high accuracy. However, the computational cost to perform inference tasks with DNNs is a challenge for mobile applications, whereas the time and energy required to train DNN models can be prohibitive even at large data centers. The computational cost of Deep Neural Networks (DNN) is dominated by memory access and multiply accumulate operations. For this reason, it has been proposed to use resistive crossbar arrays to minimize data movement and perform efficient multiply accumulate operations. These architectures store the weight value in multilevel resistive memory elements, and perform matrix-vector multiplications in the analog domain. One of the main challenges of these architectures is the limited resolution and nonlinearity of resistive memories available today. In this thesis, this limitation is addressed in two ways: by developing a model to design and optimize multilevel memories based on ferroelectric materials, and by designing an architecture to mitigate the limitations of resistive crossbars for DNN training.

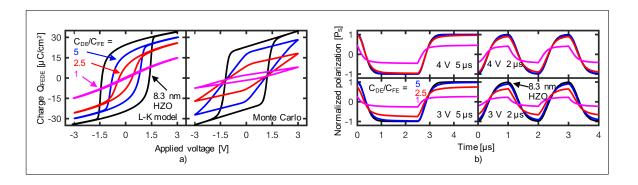

First, ferroelectrics are studied for multilevel memory devices in resistive crossbar arrays. Ferroelectrics are ceramic materials that can have two nonvolatile polarization states. In their polycrystalline form, these materials are composed of a multitude of grains with independent polarization states, allowing for dense, nonvolatile, multilevel memories compatible with standard semiconductor fabrication processes. However, modeling the dynamics of polycrystalline ferroelectrics is challenging due to the statistical variations in the composition of its grains. For this purpose, a model to extract the statistical properties of a ferroelectric film and a Monte Carlo simu-

lation that can describe and predict its polarization dynamics and variability were developed. This model provides the tools to characterize and optimize ferroelectric materials, and to design and evaluate devices, circuits and architectures for deep learning and other applications.

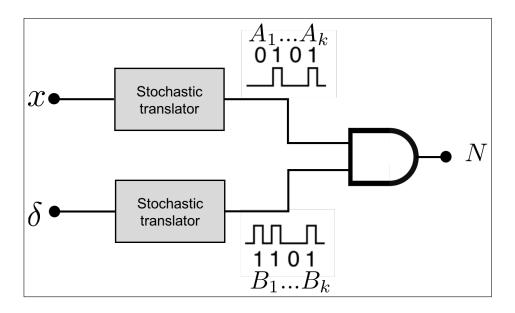

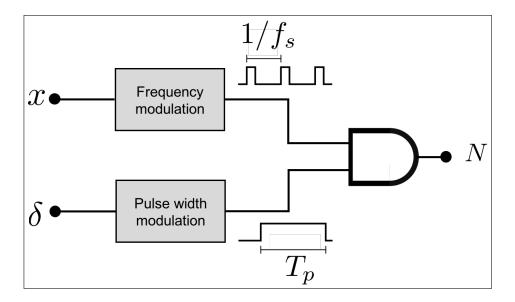

Secondly, architecture improvements to train DNN models in resistive crossbar arrays are presented. An accurate scheme for parallel weight update in resistive crossbar arrays is proposed and evaluated. By using pulse width- and frequency-modulated signals, the value of resistive elements in a crossbar array can be updated in parallel with higher accuracy than that of existing techniques based on stochastic multiplication. This scheme produces an unbiased multiplication with stochastic rounding, which is optimal for training neural networks with limited resolution. Finally, the mapping of DNN models to hardware with nonnegative weights is studied. To analyze different mapping schemes, a general vector-matrix multiplication is decomposed into a vector-matrix multiplication with nonnegative weight elements performed in a crossbar array, followed by a limited set of addition and subtraction operations described by a connection matrix. The mathematical conditions for the existence of such decomposition are derived and applied to fully connected and convolutional layers. Based on this analysis, an efficient mapping scheme is designed, which mitigates the effect of weight nonlinearity and limited resolution. These architectures are evaluated with low-level simulations of DNN training implemented in MATLAB and by extending the Keras open-source framework to incorporate nonideal weight elements and the connection matrix decomposition.

#### RESUMEN

Las redes neuronales profundas (DNN, por sus siglas en inglés) pueden realizar tareas cognitivas como el reconocimiento de voz y la detección de objetos con alta precisión. Sin embargo, el costo computacional para realizar tareas de inferencia con DNNs es un desafío para las aplicaciones móviles, mientras que el tiempo y la energía necesarios para entrenar los modelos pueden ser prohibitivos incluso en grandes centros de datos. El costo computacional de las redes neuronales profundas está dominado por multiplicaciones y acceso a memoria. Por esta razón, se ha propuesto utilizar matrices de elementos resistivos para minimizar el movimiento de datos y realizar multiplicaciones de manera eficiente en el dominio analógico. Uno de los principales desafíos de estas arquitecturas es la resolución limitada y la no linealidad de las memorias resistivas disponibles en la actualidad. En esta tesis, esta limitación se aborda de dos maneras: desarrollando un modelo para diseñar y optimizar memorias multiniveles basadas en materiales ferroeléctricos, y diseñando una arquitectura para mitigar las limitaciones de matrices resistivas para el entrenamiento de DNNs.

Primero, se estudian los dispositivos ferroeléctricos para implementar memorias multinivel. Los ferroeléctricos son materiales cerámicos que pueden tener dos estados de polarización no volátiles. En su forma policristalina, estos materiales se componen de una multitud de granos con estados de polarización independientes, lo que permite memorias densas, no volátiles y multinivel compatibles con los procesos estándar de fabricación de semiconductores. Sin embargo, modelar la dinámica de los ferroeléctricos policristalinos es un desafío debido a las variaciones estadísticas en la composición de sus granos. Para este propósito, se desarrolló un modelo para extraer

las propiedades estadísticas de un ferroeléctrico y una simulación de Monte Carlo que puede describir y predecir su dinámica de polarizacin y variabilidad. Este modelo proporciona las herramientas para caracterizar y optimizar materiales ferroeléctricos, y para diseñar y evaluar dispositivos, circuitos y arquitecturas para redes neuronales y otras aplicaciones.

En segundo lugar, se presentan mejoras en la arquitectura para entrenar modelos de redes neuronales en matrices resistivas. Se propone y evalúa un esquema preciso para la actualización de pesos en paralelo en una matriz resistiva. Al utilizar señales de ancho de pulso y modulación en frecuencia, el valor de los elementos resistivos puede actualizarse en paralelo con mayor precisión que las técnicas existentes basadas en la multiplicación estocástica. Este esquema produce una multiplicación con redondeo estocástico, que es óptimo para entrenar redes neuronales con resolución limitada. Finalmente, se estudia el mapeo de modelos de redes neuronales a hardware con pesos no negativos. Para analizar diferentes esquemas de mapeo, una multiplicación general de matrices se descompone en una multiplicación de matrices con elementos no negativos realizados en una matriz resistiva, seguida de un conjunto limitado de operaciones de suma y resta descritas por una matriz de conexiones. Las condiciones matemáticas para la existencia de esta descomposicin se derivan y aplican a modelos de redes neuronales. Sobre la base de este análisis, se diseña un esquema de mapeo eficiente, que mitiga el efecto de la no linealidad y la resolución limitada de los elementos resistivos. Estas arquitecturas se evalúan con simulaciones implementadas en MATLAB y mediante la extensión del software de código abierto Keras para incorporar elementos de peso no ideal y la descomposición de la matriz de conexiones.

# CONTENTS

| Acknow  | eledgments                                                                | ii   |

|---------|---------------------------------------------------------------------------|------|

| Figures |                                                                           | x    |

| Tables  |                                                                           | xiii |

| Chapter | r 1: Introduction                                                         | 1    |

| 1.1     | Deep neural networks                                                      | 1    |

| 1.2     | Computational cost of DNN inference                                       | 7    |

| 1.3     | Training a DNN                                                            | 10   |

| 1.4     | Hardware accelerators for DNNs                                            | 14   |

| 1.5     | Resistive crossbar accelerators                                           | 17   |

| 1.6     | Challenges to implement multilevel memory devices for training            | 20   |

| 1.7     | Objectives and hypothesis                                                 | 21   |

| 1.8     | Organization of this thesis                                               | 22   |

| Chapter | r 2: Multilevel ferroelectric memory for resistive crossbar arrays        | 24   |

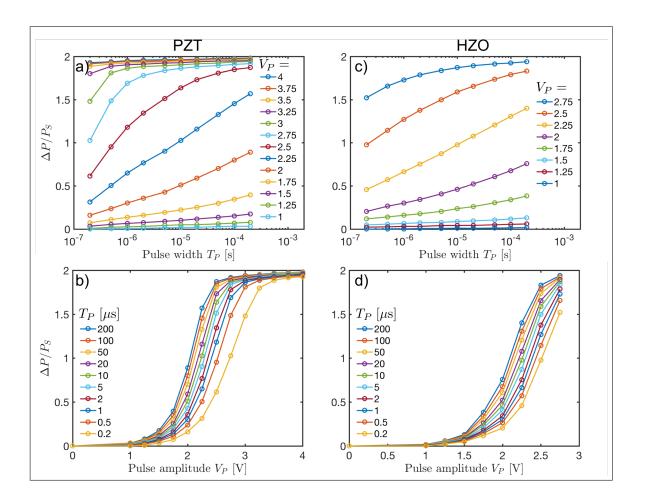

| 2.1     | Ferroelectric polarization, hysteresis loops and partial polarization     | 24   |

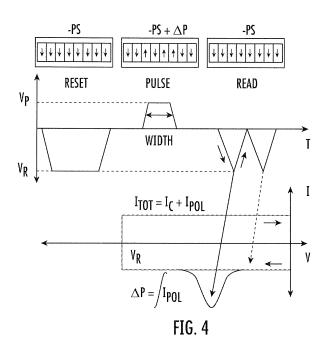

| 2.2     | Characterization of partial polarization of ferroelectric capacitors      | 27   |

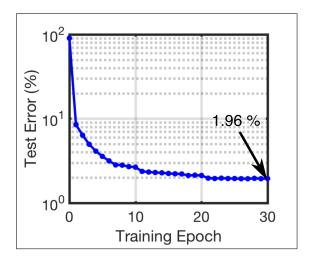

| 2.3     | Performance simulation in crossbar-based DNN accelerator                  | 29   |

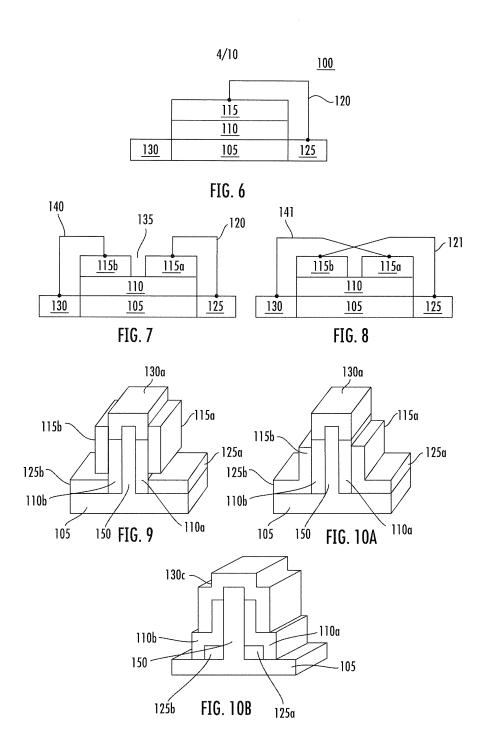

| 2.4     | Polarization-based analog memory for resistive crossbar arrays            | 31   |

| 2.5     | Conclusion                                                                | 31   |

| Chapter | r 3: Characterization and modeling of ferroelectric polarization reversal | 37   |

| 3.1     | Polarization reversal in a ferroelectric crystal                          | 37   |

| 3.2     | Nucleation-limited switching in polycrystalline ferroelectrics            | 39   |

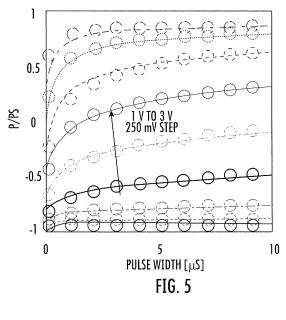

| 3.3     | Experimental results and parameter extraction                             | 42   |

| 3.4     | Study of thickness dependence in ferroelectric HZO capacitors             | 47   |

| 3.5     | Conclusion                                                                | 49   |

| Chapter | r 4: Monte Carlo simulation of polarization dynamics in polycrystalline   |      |

| ferro   | pelectrics                                                                | 51   |

| 4.1     | Revisit NLS model and nucleation rate                                     | 52   |

| 4.2     | Monte Carlo simulation of polarization reversal                           | 55   |

| 4.3     | Monte Carlo simulation for arbitrary input waveforms                      | 57   |

| 4.4     | Accumulation and relaxation of the history-dependent switching rate     | 61  |

|---------|-------------------------------------------------------------------------|-----|

| 4.5     | Model predictions                                                       | 64  |

| 4.6     | Conclusion                                                              | 66  |

| -       | r 5: Parallel weight update in resistive crossbar arrays by local modu- |     |

| latio   | on of pulse width and frequency                                         | 68  |

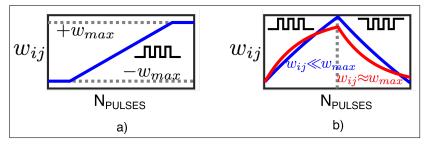

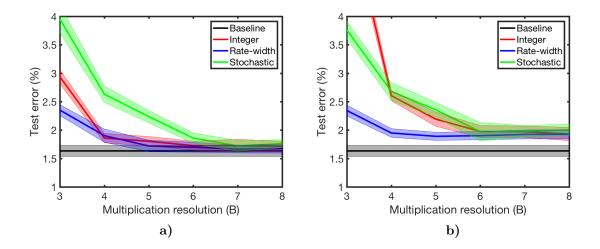

| 5.1     | Analysis of stochastic multiplication                                   | 69  |

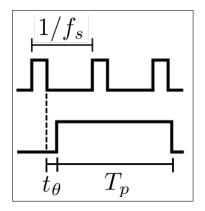

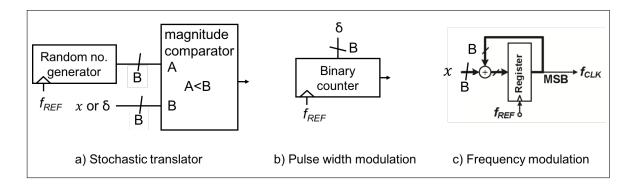

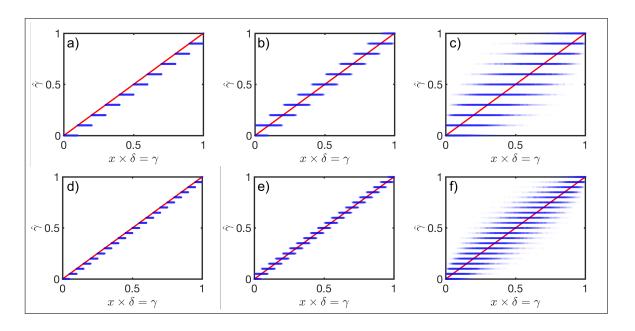

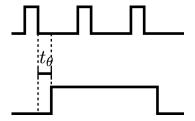

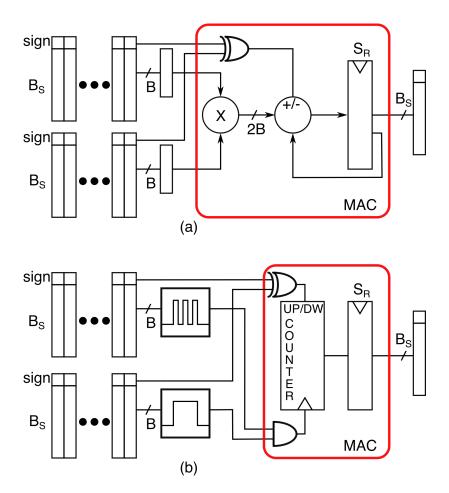

| 5.2     | Multiplication by pulse width and frequency modulation                  | 71  |

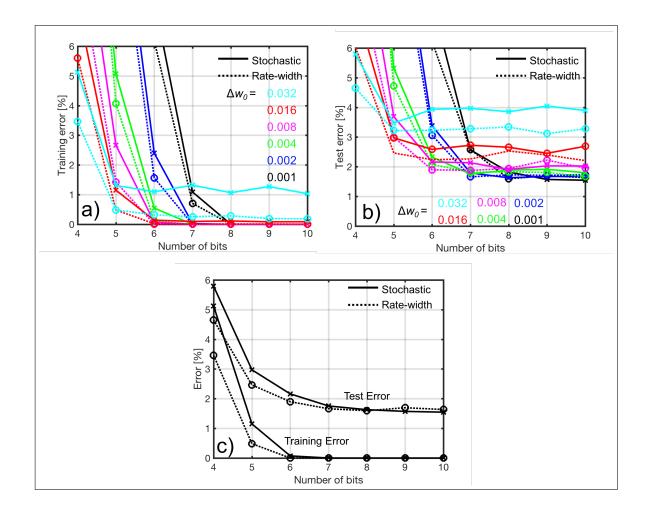

| 5.3     | Comparison of stochastic and rate-width multiplication                  | 73  |

|         | 5.3.1 Hardware resources                                                | 73  |

|         | 5.3.2 Multiplication accuracy                                           | 74  |

| 5.4     | Performance evaluation in a resistive crossbar array                    | 75  |

| 5.5     | Conclusion                                                              | 77  |

| _       | r 6: Efficient mapping of neural network models to resistive crossbar   |     |

|         | sys with limited weight resolution                                      | 78  |

| 6.1     | Prior approaches to map DNN model to resistive crossbar arrays          | 78  |

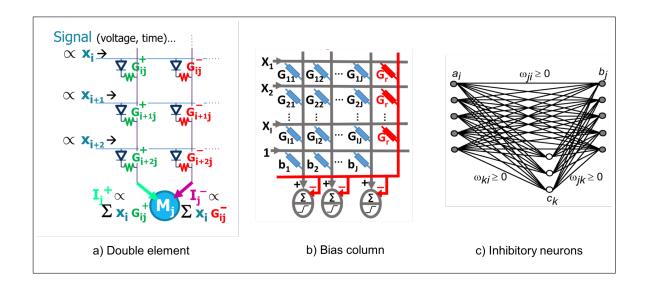

| 6.2     | Connection matrix decomposition for fully-connected layers in a resis-  |     |

|         | tive crossbar array                                                     | 81  |

|         | 6.2.1 Sufficient conditions for existence                               | 82  |

|         | 6.2.2 Implementation in a crossbar array                                | 84  |

| 6.3     | Connection Matrix decomposition applied to convolutional layers         | 87  |

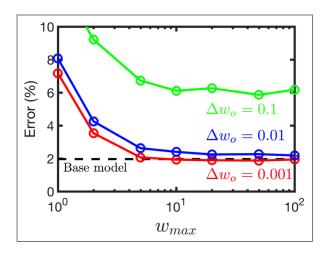

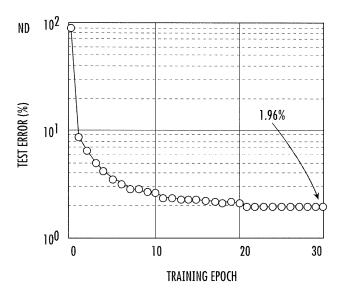

| 6.4     | Experimental validation with MNIST and CIFAR-10 datasets                | 88  |

| 6.5     | Evaluation with limited weight resolution and nonlinearity              | 95  |

| 6.6     | Conclusion                                                              | 99  |

| Chapte  | r 7: Conclusion                                                         | 100 |

| Bibliog | raphy                                                                   | 104 |

| Append  | lix A: List of publications and patents                                 | 118 |

| Append  | lix B: US patent application number 16180453                            | 120 |

|         | dix C: Counter-based neural network architecture with rate-width mul-   |     |

| -       | ication                                                                 | 149 |

| C.1     | Statistical analysis                                                    | 151 |

|         | C.1.1 Stochastic pulse multiplication                                   | 151 |

| <u></u> | C.1.2 Rate-width multiplication                                         | 153 |

| C.2     |                                                                         | 154 |

| C.3     | i                                                                       | 156 |

| C.4     | Conclusion                                                              | 159 |

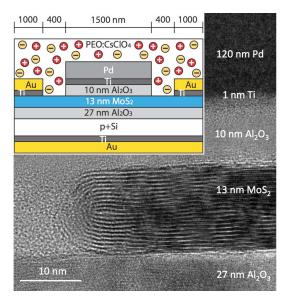

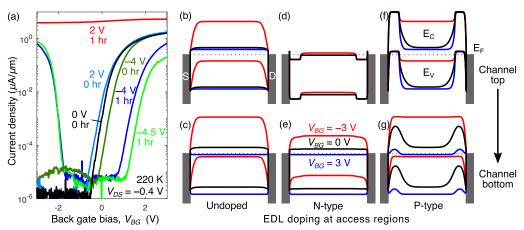

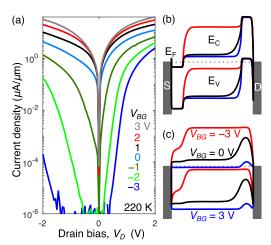

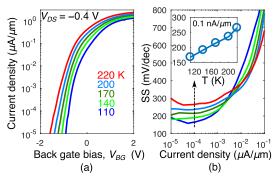

| Appendix D: Reconfigurable electric double layer doping in an $MoS_2$ nanorib- |     |

|--------------------------------------------------------------------------------|-----|

| bon transistor                                                                 | 161 |

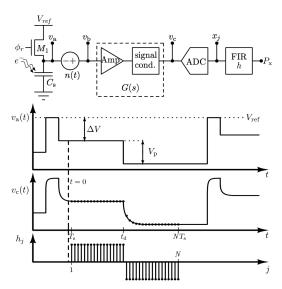

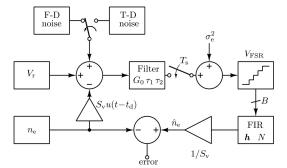

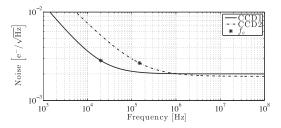

| Appendix E: Optimal CCD readout by digital correlated double sampling          | 168 |

# FIGURES

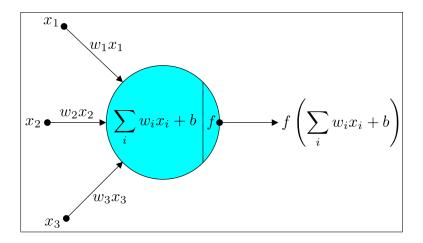

| 1.1  | Diagram of a neuron: the basic computational unit of a neural network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

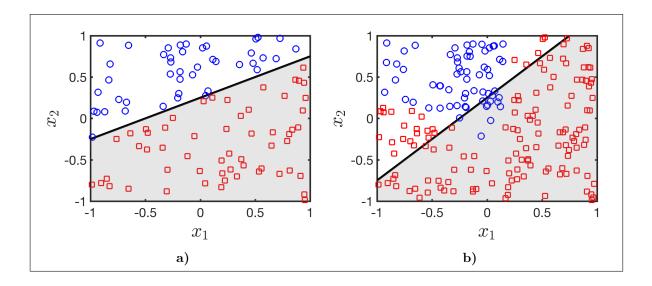

| 1.2  | Logistic regression implemented with a single neuron with binary threshold activation function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3  |

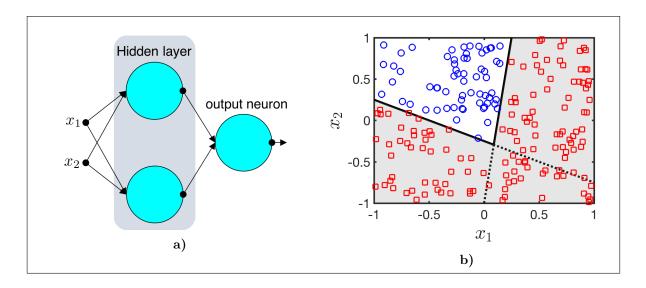

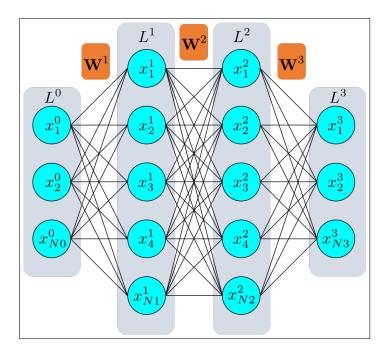

| 1.3  | Neural network formed by a sequence of two layers of neurons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4  |

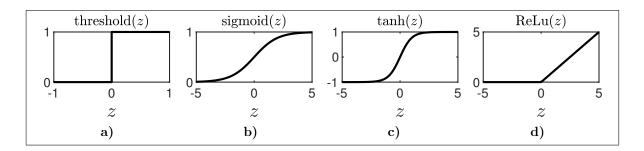

| 1.4  | Commonly used activation functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5  |

| 1.5  | Example 4-layer fully connected DNN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6  |

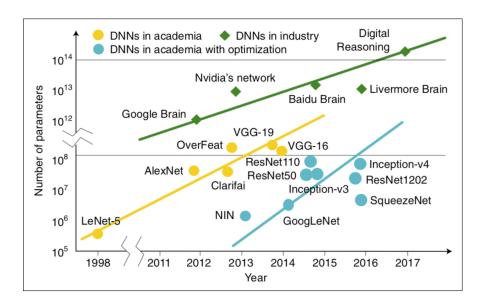

| 1.6  | Exponential increase in DNN parameter number over time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9  |

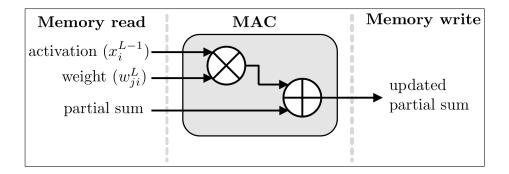

| 1.7  | Diagram of MAC operation and memory access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9  |

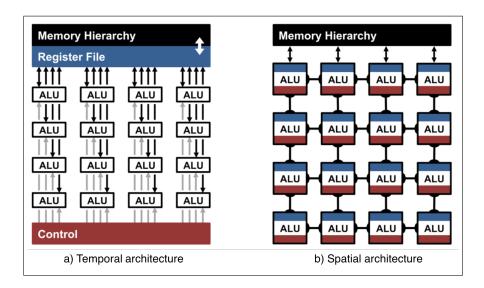

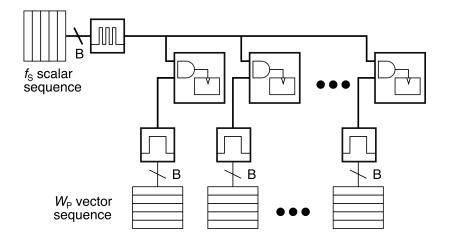

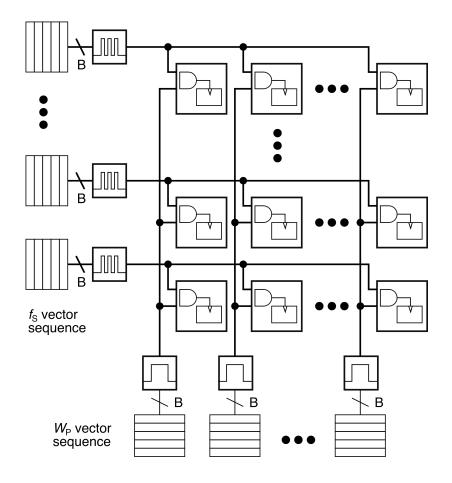

| 1.8  | Temporal and spatial architecture paradigms for highly parallel operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16 |

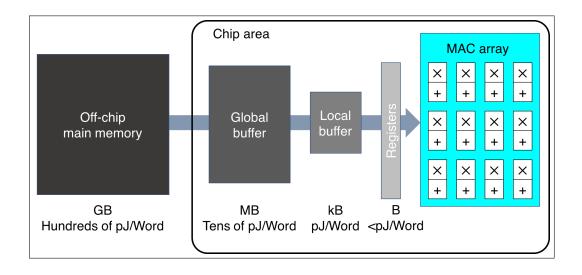

| 1.9  | Memory hierarchy and MAC array in a DNN accelerator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16 |

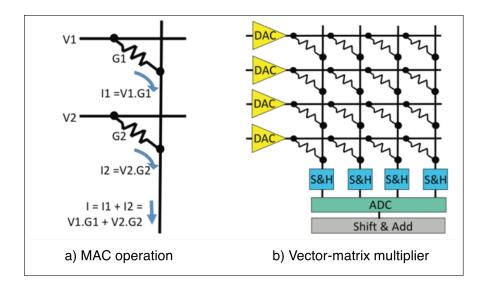

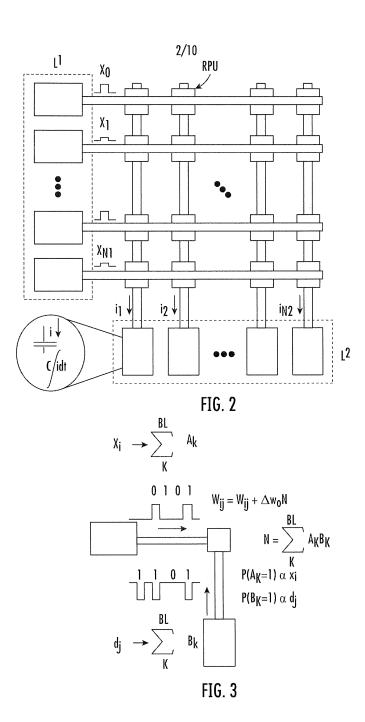

| 1.10 | Crossbar implementation of matrix-vector multiplication for acceleration of DNNs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 17 |

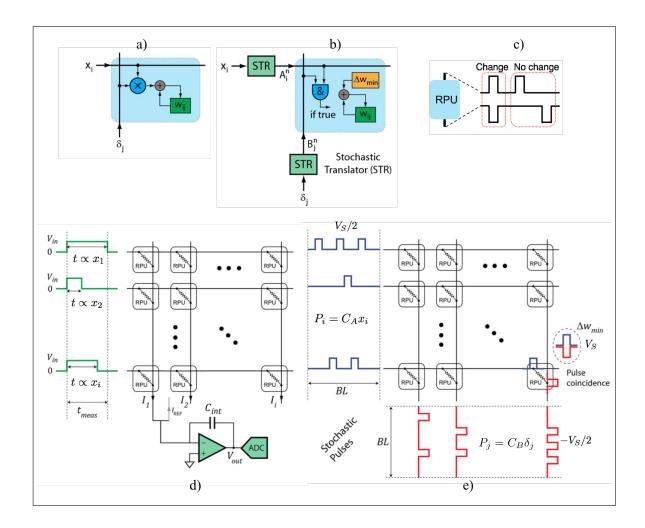

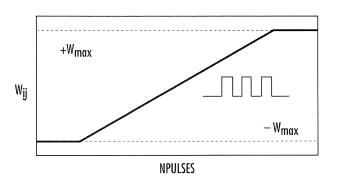

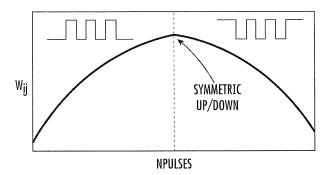

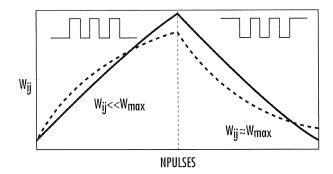

| 1.11 | Resistive processing unit operating principle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 19 |

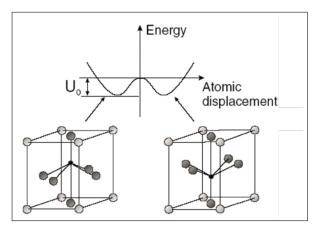

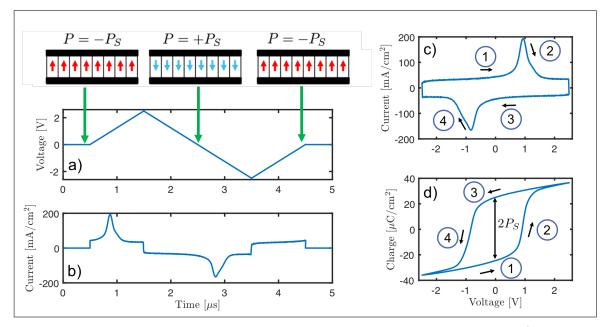

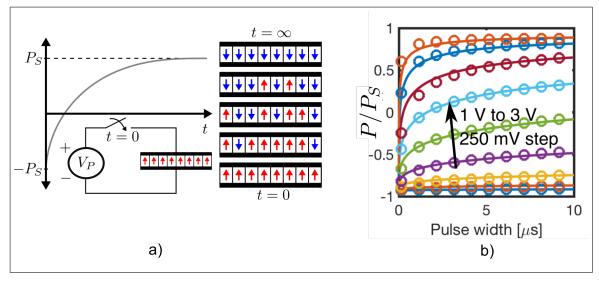

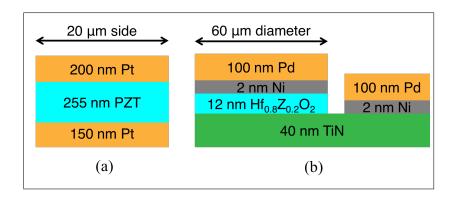

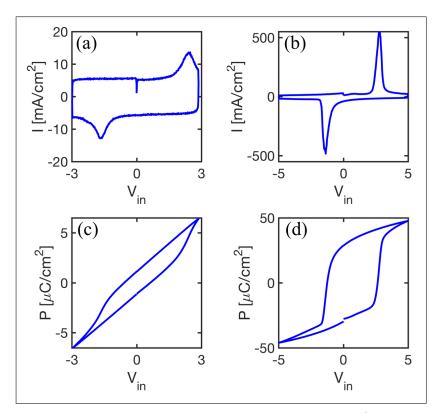

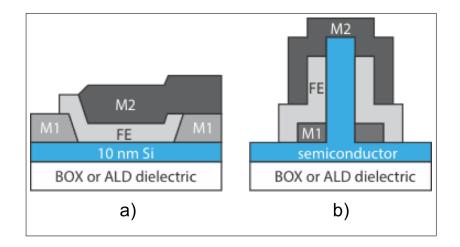

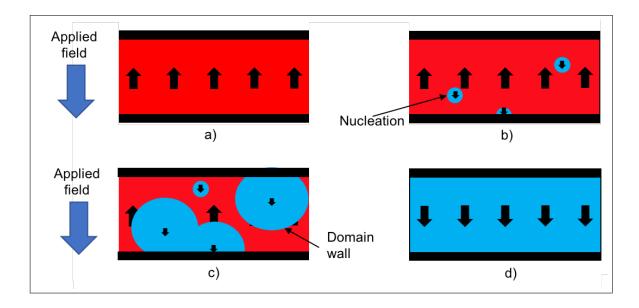

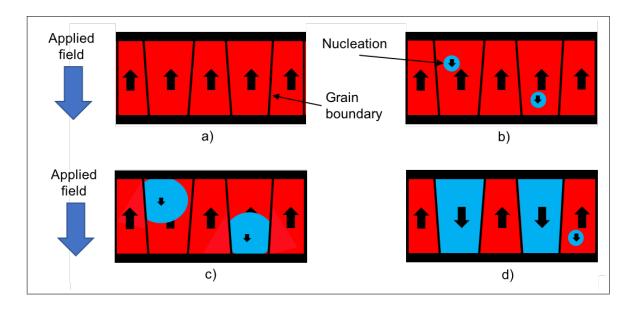

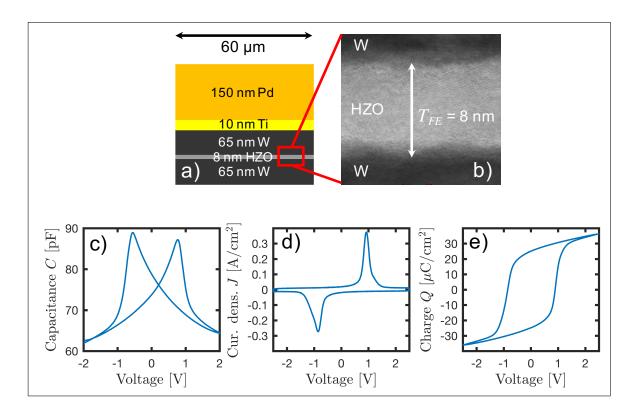

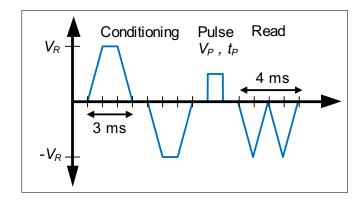

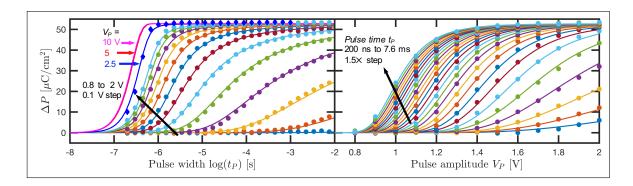

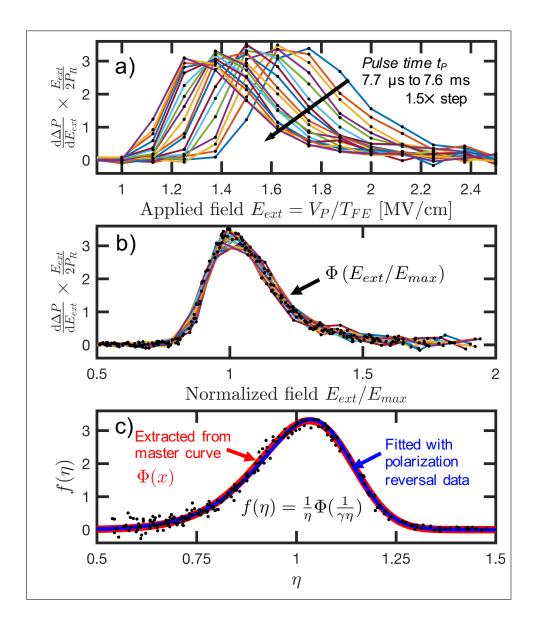

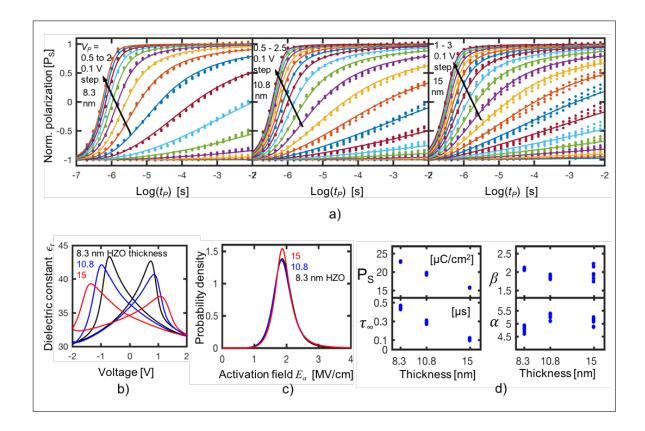

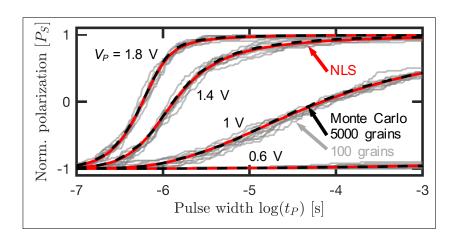

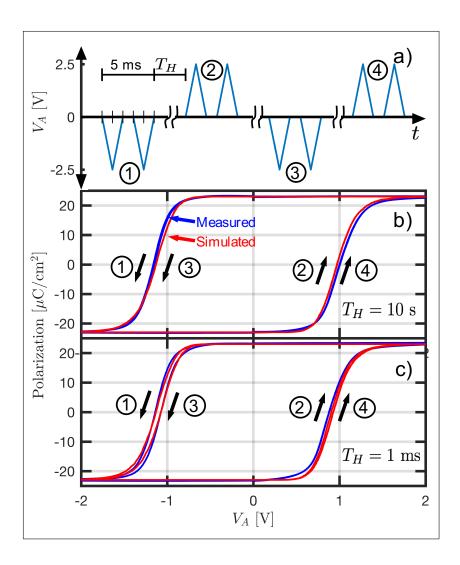

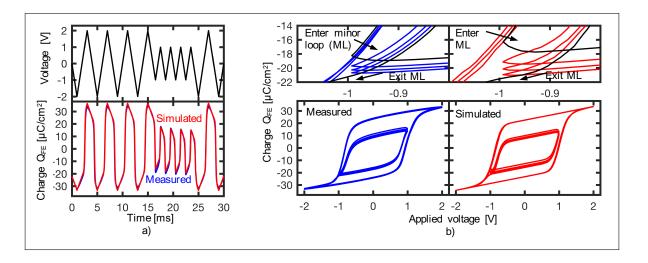

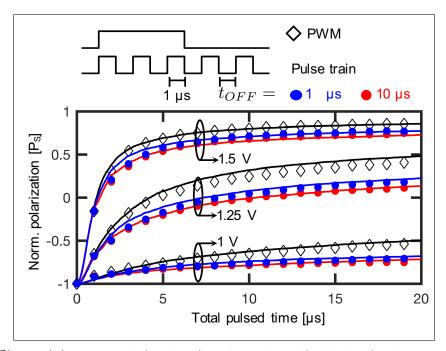

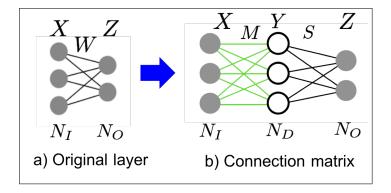

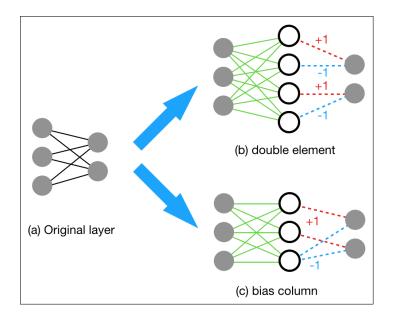

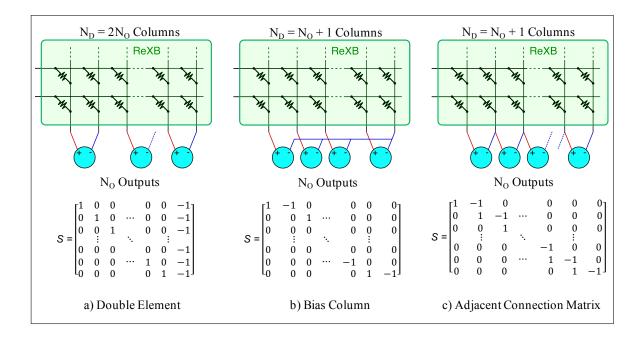

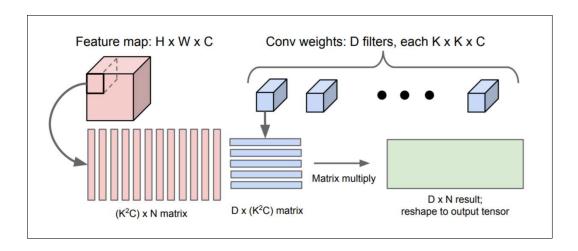

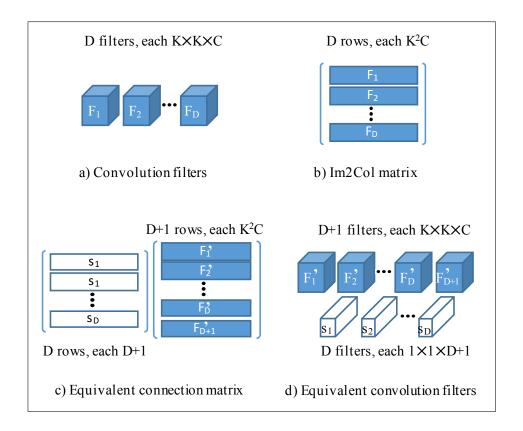

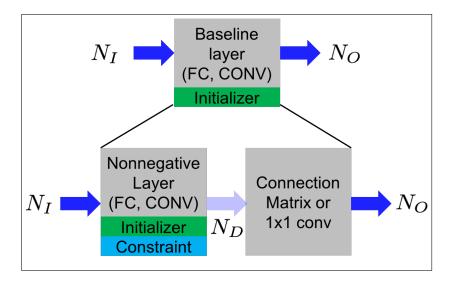

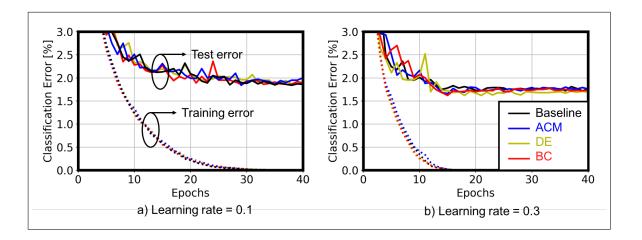

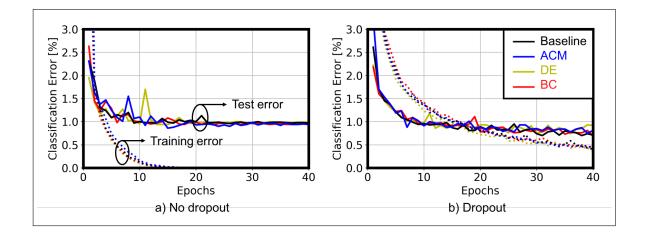

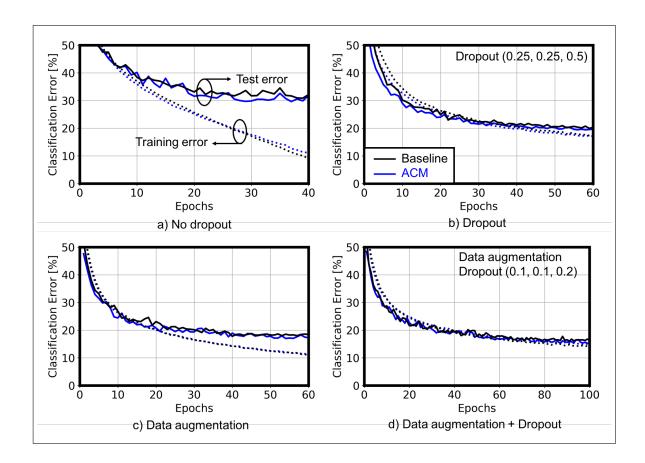

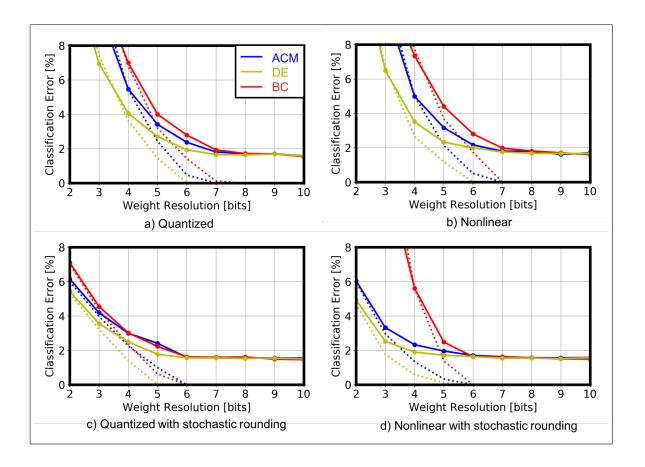

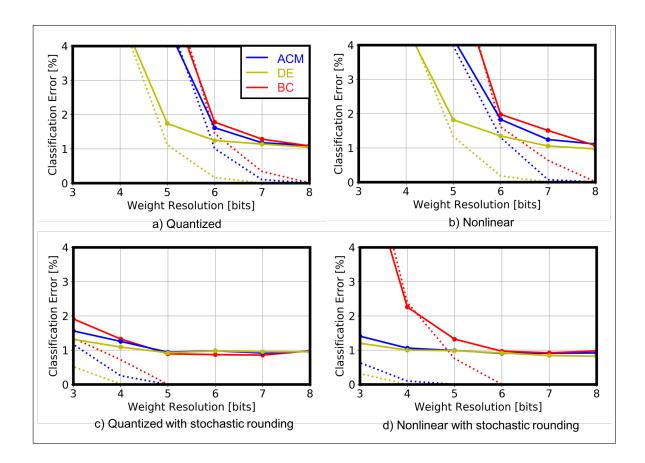

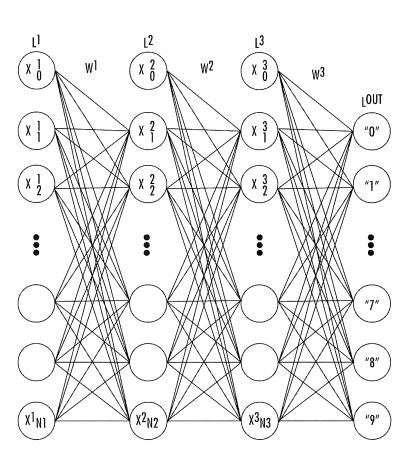

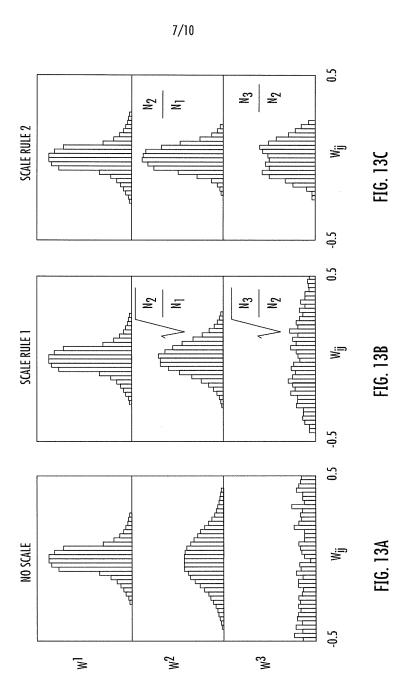

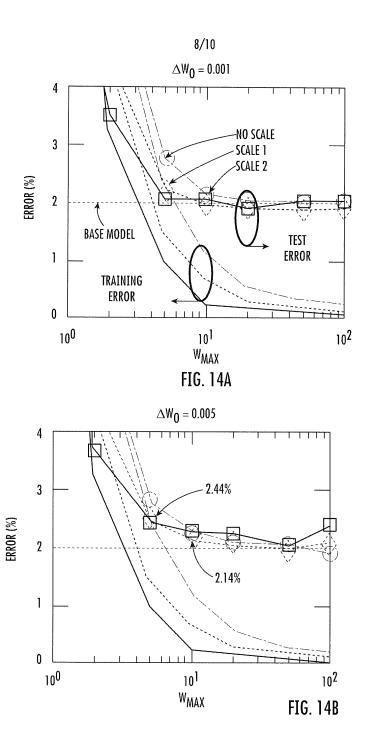

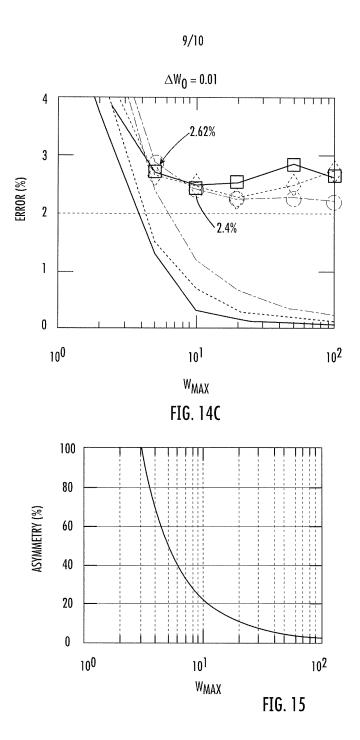

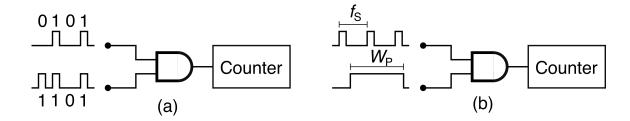

| 2.1  | Ferroelectric permanent dipole moment in a noncentrosymmetric per-<br>ovskite unit cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24 |